|

gccDppConsole Test C++ SDK

20170920

DPP C++ Console Demonstration

|

|

gccDppConsole Test C++ SDK

20170920

DPP C++ Console Demonstration

|

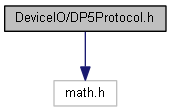

#include <math.h>

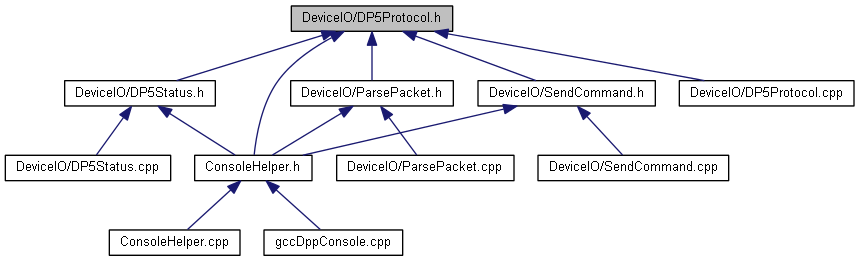

Go to the source code of this file.

| #define ACK 0 |

Definition at line 260 of file DP5Protocol.h.

| #define ETHERNET 2 |

Definition at line 268 of file DP5Protocol.h.

| #define ETHERNET_TIMEOUT 1000 |

Definition at line 270 of file DP5Protocol.h.

| #define MAX_BUFFER_DATA 8192 |

Definition at line 293 of file DP5Protocol.h.

| #define MAX_SCOPE_DATA 2048 |

Definition at line 294 of file DP5Protocol.h.

| #define Retries 2 |

Definition at line 274 of file DP5Protocol.h.

| #define RS232 0 |

Definition at line 266 of file DP5Protocol.h.

| #define RS232_TIMEOUT 2500 |

Definition at line 271 of file DP5Protocol.h.

| #define SYNC1_ 0xF5 |

Definition at line 263 of file DP5Protocol.h.

| #define SYNC2_ 0xFA |

Definition at line 264 of file DP5Protocol.h.

| #define USB 1 |

Definition at line 267 of file DP5Protocol.h.

| #define USB_DiagDataDelayMS 2500 |

Definition at line 295 of file DP5Protocol.h.

| #define USB_TIMEOUT 500 |

Definition at line 272 of file DP5Protocol.h.

| typedef struct _Packet_In Packet_In |

| enum PID1_TYPE |

Definition at line 98 of file DP5Protocol.h.

| enum PID2_ACK_TYPE |

Definition at line 237 of file DP5Protocol.h.

| enum PID2_RCV_SCA_TYPE |

Definition at line 233 of file DP5Protocol.h.

Definition at line 218 of file DP5Protocol.h.

Definition at line 203 of file DP5Protocol.h.

| enum PID2_RCV_STATUS_TYPE |

Definition at line 199 of file DP5Protocol.h.

| enum PID2_REQ_CONFIG_TYPE |

Definition at line 149 of file DP5Protocol.h.

Definition at line 155 of file DP5Protocol.h.

| enum PID2_REQ_SCA_TYPE |

Definition at line 143 of file DP5Protocol.h.

Definition at line 130 of file DP5Protocol.h.

| PID2_SEND_SPECTRUM | |

| PID2_SEND_CLEAR_SPECTRUM | |

| PID2_SEND_SPECTRUM_STATUS | |

| PID2_SEND_CLEAR_SPECTRUM_STATUS |

Definition at line 118 of file DP5Protocol.h.

| enum PID2_REQ_STATUS_TYPE |

Definition at line 114 of file DP5Protocol.h.

| enum PID2_VENDOR_REQ_TYPE |

Definition at line 169 of file DP5Protocol.h.

| enum TRANSMIT_PACKET_TYPE |

Definition at line 5 of file DP5Protocol.h.

1.7.6.1

1.7.6.1