# AMD Geode<sup>™</sup> GX1 Processor/ CS5530A Companion Device Power Management Implementations

# 1.0 Scope

The intention of this document is to fully describe the power management features available when designing systems based on the AMD Geode<sup>™</sup> GX1 processor and AMD Geode<sup>™</sup> CS5530A companion device. Once armed with a detailed understanding of the power management features available, the system designer should then be able to develop an optimized design from the power consumption standpoint. The AMD Geode<sup>™</sup> SP4GX10 (GX1/CS5530A) system platform is used as an example of a specific implementation for this application note.

The GX1 processor and CS5530A companion device contain advanced power management features for reducing the power consumption of the system. The hardware resources provided by a combined GX1/CS5530A-based system support a full-featured power management implementation.

The SP4GX10 system platform incorporates a wide range of power management functions and features. Power management can be enabled through the use of hardware features as well as power management-aware software. Hardware support includes peripheral and activity monitors via user selectable timers and CPU Suspend and Suspend Modulation support. Software control is primarily via the APM (Advanced Power Management) compliant XpressROM BIOS. XpressROM supports the APM specification version 1.2 and can be further tailored to meet the specific requirements of a particular system design.

# 2.0 Introduction

This application note discusses power management from three different viewpoints. First, device and system power management states of the GX1 processor and CS5530A companion device are discussed. Then, specific SP4GX10 mode programming for power management of a system is provided. Finally, power management of peripherals, such as disk drives and displays, is discussed.

The application note consolidates numerous register programming tables from the device data books and includes them here for easy reference. Detailed designers are invited to review the most recent editions of these data books on the AMD Geode<sup>™</sup> Developers Support web site to ensure they are using the latest information.

Two basic methods are supported to manage power during periods of inactivity. The first method, called activity based power management, allows the hardware in the CS5530A to monitor activity to certain devices in the system, and if a period of inactivity occurs, take some form of power conservation action. This method does not require OS (operating system) support because it is handled by SMM (System Management Mode) software. Simple monitoring of external activity is imperfect as well as inefficient.

The second method, called passive power management, requires the OS to take the active role in managing power. AMD supports two APIs (application programming interfaces) to enable power management by the OS: APM (Advanced Power Management) and ACPI (Advanced Configuration and Power Interface). The extent to which these resources are employed depends on the application and the discretion of the system designer.

# 2.1 Power Management Features

Power management resources can be grouped according to the function they enable or support. The major functions are as follows:

### **Power States**

- GX1 Processor/CS5530A Companion Device Power States:

- System Management Mode (SMM)

- Suspend-on-Halt (Active Idle)

- CPU Suspend

- Suspend Modulation

- 3 Volt Suspend

- System Platform Power States:

- Mechanical Off State

- Off State

- Working State

- Full-On Mode

- Doze Mode

- Standby Mode

- Suspend Mode

- Save-to-Disk/Save-to-RAM

#### SP4GX10 System Platform Working State Modes

• Mode Definitions and Programming

#### **Peripheral Power Management**

- Device Idle Timers and Traps

- General Purpose Timers

- Power Management SMI Status Reporting Registers

- Device and Peripheral Power States

# 3.0 Device Interconnections

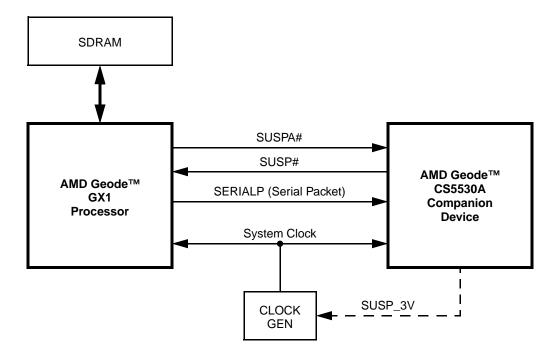

Figure 3-1 shows the recommended device interconnections. The dashed line marked SUSP\_3V is intended to be used to stop the system clocks during the 3 Volt Suspend state; it connects to the INHIBIT pin of the system clock generator. Designs not requiring the 3 Volt Suspend state should not implement this connection.

## 3.1 GX1 Processor Serial Packet Interface

The power management logic of the GX1 processor provides the CS5530A companion with information regarding CPU status. The majority of the system power management logic is implemented in the CS5530A, but a minimal amount of logic is contained within the GX1 to provide information that is not externally visible (e.g., graphics controller status).

The GX1 implements a simple serial communications mechanism to transmit the CPU status to the CS5530A. The GX1 accumulates CPU events in an 8-bit read-only register, "PM Serial Packet" register (GX\_BASE+Memory Offset 850Ch), that is serially transmitted out of the GX1 every 1 to 10  $\mu$ s. The transmission frequency is set with bits [4:3] of the PM Serial Packet Control register within the GX1. (See Table 8-1 "GX1 Processor Power Management Serial Packet Register" on page 36 for complete bit descriptions.)

The packet transmitter holds the serial output pin (SERI-ALP) low until the transmission interval timer has elapsed. Once the timer has elapsed, the SERIALP pin is held high for two clocks to indicate the start of packet transmission. The contents of the Serial Packet Register are then shifted out starting from bit 7 down to bit 0. The SERIALP pin is held high for one clock to indicate the end of packet transmission and then remains low until the next transmission interval. After the packet transmission is complete, the Serial Packet Register's contents are cleared.

The input clock of the GX1 processor is used as the clock reference for the serial packet transmitter.

Once a bit in the register is set, it remains set until the completion of the next packet transmission. Successive events of the same type that occur between packet transmissions are ignored. Multiple unique events between packet transmissions accumulate in this register. The processor transmits the contents of the serial packet only when a bit in the Serial Packet Register is set and the interval timer has elapsed.

The CS5530A companion device decodes the serial packet after each transmission and performs the power management tasks related to video retrace.

Figure 3-1. Device Interconnections

# 4.0 Power States

This chapter is divided into two main sections describing the GX1 processor and CS5530A companion device power states and the SP4GX10 system platform power states.

# 4.1 GX1 Processor/CS5530A Companion Device Power States

The GX1 processor and CS5530A companion device have a variety of power management features and states. In this section, these features are described in detail from the perspective of the devices themselves. In the next major section, these same states are discussed from the system perspective.

#### 4.1.1 Enabling Power Management

Both the GX1 and the CS5530A have global power management enable controls that must be properly set up to enable their power management features.

GX1: Index C2h[7] must be set to 1 for the SUSP# input and SUSPA# output to function. Index C3h[3] must be set to 1 if the SUSP# input is to be recognized while in SMM mode. (See Table 8-2 "GX1 Processor Suspend Mode Related Bits" on page 37 for bit description.)

CS5530A: F0 Index 80h[0] must be set to 1 to enable the SUSP#/SUSPA# handshake. Other bits in this register may also be set depending on which power management features are desired. (See Table 8-3 "CS5530A Suspend/Suspend Modulation Configuration Related Registers" on page 38 for details.)

The CS5530A has a bit located at F0 Index 96h[4], called the "Power Savings Mode" bit. Although the data book indicates that this bit can be used to enable and disable power management, this is not the case. The referenced bit should always be cleared to 0, and should never be used to enable or disable power management.

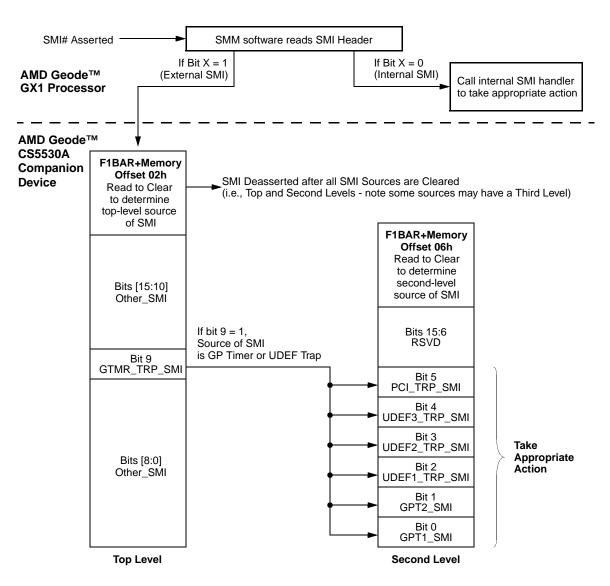

#### 4.1.2 System Management Mode

The GX1 processor has an operational mode called SMM, System Management Mode. This mode is generally entered when the SMI# pin goes active. If active power management is desired, then the CS5530A is programmed at boot time to activate SMM through the SMI# pin due to specific I/O inactivity.

SMM is also used in the passive power management method, however, it is limited to supporting specific API calls such as entering Sleep modes.

The GX1 processor must be enabled to recognize the SUSP# input while in SMM. Refer to Section 4.1.1 "Enabling Power Management" for enabling information.

### 4.1.3 Suspend-on-Halt

Suspend-on-Halt, also known as the Active Idle state, is the most effective power-reducing feature of the GX1 processor. Suspend-on-Halt allows the system to reduce power when the system's OS becomes idle without introducing any delay when the system's OS becomes active again. The processor's core clock is stopped in this state and therefore, considerable power is saved in the processor.

Before entering Suspend-on-Halt, it must be enabled. Set GX1 Index C2h[3] to 1 to allow this state to occur. (See Table 8-2 on page 37 for bit description.)

To enter this state, the GX1 executes a HLT (Halt) instruction and asserts the SUSPA# signal in response. The operating system has control of the entry of this state because the OS has either executed HLT or made a BIOS call to indicate idle, and the BIOS executed the HLT instruction. When entered, Suspend-on-Halt stops the clock to the processor core while the integrated functions (graphics, memory controller, PCI controller) are still active. The CS5530A takes advantage of this power state by stopping the clock to some of the internal circuitry.

There is no observational evidence that the processor has changed operational behavior except for two things. The GX1 draws significantly less core power and the SUSPA# output pin is active while in this state.

The CS5530A can still make bus master requests for IDE, audio, USB, and ISA from this state. When the CS5530A or any other device on the PCI bus asserts REQ#, the GX1 deasserts SUSPA# for the duration of REQ# activity. Once REQ# has become inactive and all PCI cycles have stopped, the GX1 reasserts SUSPA#. SUSPA# remains active until the GX1 receives an INTR or SMI event that ends the CPU Halt condition.

### 4.1.4 CPU Suspend

CPU Suspend is a hardware initiated power management state. This state is similar to Suspend-on-Halt except for its entry and exit method; power savings is identical to Suspend-on-Halt. The GX1 enters this state in response to the CS5530A asserting SUSP#. The GX1 asserts the SUSPA# pin in response to indicate that the processor has entered CPU Suspend. As in Suspend-on-Halt, the processor temporally disables CPU Suspend when there is PCI master activity.

To prepare for this state, set GX1 Index C2h[7] to 1, which enables the SUSP# input and the SUSPA# output. Also, set GX1 Index C3h[3] to 1, which enables the GX1 to respond to the SUSP# signal while in SMM.

To enter Suspend, trigger a Suspend state from the CS5530A (see Section 4.1.7 "Triggering Suspend State" on page 6). The GX1 will complete its current cycle and assert SUSPA# in response.

The CS5530A deasserts SUSP# when a wakeup INTR or SMI event occurs. The Suspend Configuration register (CS5530A F0 Index BCh) is shown in Table 8-3 on page 38 along with other related Suspend/Suspend Modulation configuration registers.

#### 4.1.5 Suspend Modulation

Suspend Modulation is a derivative of the On and Suspend states and works by asserting and deasserting the SUSP# pin to the CPU for a configurable period and duty cycle. By modulating the SUSP# pin, an effective reduction in frequency is achieved. Certain processing activities (SMI#, interrupts, and VGA activity) can be monitored by the CS5530A to temporarily interrupt Suspend Modulation for a programmable amount of time.

Suspend Modulation is the system power management choice of last resort. However, it is an excellent choice for thermal management. If the system is expected to operate in a thermal environment where the processor could overheat, then Suspend Modulation can be used to reduce power consumption in the overheated condition and thus reduce the processor's temperature.

When used as a power management state, Suspend Modulation works by assuming that the processor is idle unless external activity indicates otherwise. This approach effectively slows down the processor until external activity indicates a need to run at full speed, thereby reducing power consumption.

Suspend Modulation serves as the primary CPU power management mechanism when APM or some other power management software strategy is not present. It can also act as a backup for situations where the power management scheme does not correctly detect an Idle condition in the system.

In order to provide high-speed performance when needed, the SUSP# pin modulation can be temporarily disabled any time system activity is detected. When this happens, the processor is "instantly" converted to full speed for a programmed duration. System activities in the CS5530A are defined in hardware as: any unmasked IRQ, accessing Port 061h, SMI, and/or accessing the graphics controller. Since the graphics controller is integrated in the GX1, the indication of graphics activity is sent to the CS5530A via the serial link (see Section 3.1 "GX1 Processor Serial Packet Interface" on page 2) and is automatically decoded. Graphics activity is defined as any access to the VGA register space, the VGA frame buffer, the graphics accelerator control registers and the configured graphics frame buffer. The automatic speedup events (IRQ, SMI, and/or graphics) for Suspend Modulation should be used together with software-controlled speedup registers for major I/O events such as any access to the floppy disk controller, hard disk drive, or parallel/serial ports, since these are indications of major system activities. When major I/O events occur, Suspend Modulation can be temporarily disabled using the procedures described in the following subsections.

Bus master internal (Ultra DMA/33, Audio, USB, or ISA) or external requests do not directly affect the Suspend Modulation programming.

#### 4.1.5.1 Suspend Modulation for Thermal Management

The best use of Suspend Modulation is for thermal management. If the system exceeds temperature limits in extreme conditions, then thermal management by use of Suspend Modulation can be easily and effectively used to reduce system cost by eliminating fans and possibly also heatsinks. However, if maximum performance is required in all conditions then Suspend Modulation should not be used, since invoking Suspend Modulation imposes a performance penalty.

Using an external circuit based on National Semiconductor's LM84 temperature sensor or similar device, the CS5530A can monitor the temperature of the system and/or CPU, and assert the SMI# pin if the system or CPU exceeds a predefined high limit. The power management SMM handler then enables Suspend Modulation, allowing the processor or system to cool off. When the temperature drops back below a predefined low limit, the CS5530A again asserts the SMI# pin. The power management SMM handler disables Suspend Modulation and normal operation resumes.

#### 4.1.5.2 Suspend Modulation for Power Management

Suspend Modulation can also be used for a crude method of power management. The CS5530A monitors I/O activity and when that monitoring indicates inactivity, the CS5530A asserts the SMI# pin. The power management SMM handler enables Suspend Modulation. When I/O activity picks up, the SMI# pin is asserted again and the power management SMM handler exits Suspend Modulation and normal operation resumes.

#### 4.1.5.3 Configuring Suspend Modulation

Control of the Suspend Modulation feature is accomplished using the CS5530A's Suspend Modulation OFF Count Register, Suspend Modulation ON Count Register, and Suspend Configuration Register (F0 Index 94h, 95h, and 96h, respectively). The CS5530A Power Management Enable Register 1 (F0 Index 80h) contains the enables for the individual activity speedup timers.

Bit 0 of the Suspend Configuration Register (F0 Index 96h) enables the Suspend Modulation feature. Bit 1 controls how SMI events affect the Suspend Modulation feature. In general this bit should be set to a 1, which causes SMIs to disable Suspend Modulation until it is re-enabled by the SMI handler.

The CS5530A Suspend Modulation OFF and ON Count Registers (F0 Index 94h and 95h) control two 8-bit counters that represent the number of 32  $\mu$ s intervals that the SUSP# pin is asserted and then deasserted to the processor. These counters define a ratio that is the effective frequency of operation of the system while Suspend Modulation is enabled.

$$F_{eff} = F_{GX86} x \qquad \frac{Off Count}{On Count + Off Count}$$

The IRQ and Video Speedup Timer Count registers (CS5530A F0 Index 8Ch and 8Dh) configure the amount of time that Suspend Modulation is disabled when the respective events occur.

#### 4.1.5.4 SMI Speedup Disable

If the Suspend Modulation feature is being used for CPU power management, the occurrence of an SMI disables the Suspend Modulation function so that the system operates at full speed while in SMM. There are two methods used to invoke this via bit 1 of the Suspend Configuration Register.

If F0 Index 96h[1] = 0: Use the CS5530A IRQ Speedup Timer (F0 Index 8Ch) to temporarily disable Suspend Modulation when an IRQ occurs.

If F0 Index 96h[1] = 1: Disable Suspend Modulation when an SMI occurs until a read to the SMI Speedup Disable Register (F1BAR+Memory Offset 08h) occurs.

The CS5530A SMI Speedup Disable Register prevents Virtual System Architecture (VSA) technology software from entering Suspend Modulation while operating in SMM. The data read from this register can be ignored. If the Suspend Modulation feature is disabled, reading this I/O location has no effect. Table 8-3 on page 38 shows the bit formats of the Suspend Modulation related registers.

#### 4.1.6 3 Volt Suspend

3 Volt Suspend is a non-operational state, and is a lower system power state than CPU Suspend. This state is usually used to put the system into a deep sleep to conserve power and still allow the user to resume where they left off. In a system designed to take full advantage of this mode (such as the SP4GX10), not only is the processor in the Suspend mode, but the graphics pipeline is disabled, the system SDRAMs are in a low-power self refresh state, and the processor's core clock has been stopped. Figure 3-1 "Device Interconnections" on page 2, shows (as a dashed line) the connection required between the CS5530A and the system clock generator to allow system clock stopping.

To prepare to enter this state:

- Set the CLK\_STP bit in the GX1 PM\_CNTRL\_CSTP register (GX\_BASE+Memory Offset 8508h[0] = 1).

- Set the CPU Clock Stop bit in the CS5530A Clock Stop Control Register (F0 Index BCh[0] = 1).

- Turn off the graphics pipeline (GX\_BASE+Memory Offset 8304h[0] = 0).

The only function of the CLK\_STP bit in the GX1 is to force the memory controller in the GX1 to put the SDRAMs into a self refresh mode upon acknowledgement of a SUSP# input. If CLK\_STP is set and the graphics pipeline is still active, then the SUSP# is ignored and 3 Volt Suspend is not entered.

Upon programming completion, trigger a Suspend state from the CS5530A (see Section 4.1.7 "Triggering Suspend State" on page 6). A SUSP#/SUSPA# handshake cycle will occur, and then the 3 Volt Suspend state will occur. When 3 Volt Suspend is entered, the GX1 memory controller puts the SDRAMs in self refresh mode. Once SUSPA# has gone active, the SYSCLK input pin to the GX1 can also be stopped via the INHIBIT control on the clock generator.

The CS5530A supports the stopping of the CPU and system clocks in the 3 Volt Suspend state. The CS5530A asserts the SUSP\_3V pin after it has gone through the SUSP#/SUSPA# handshake with the GX1. The SUSP\_3V pin is a state indicator, indicating that the system is in a low-activity state. This indicator can be used to put the system into a low-power state (the system clock can be turned off). The CS5530A's SUSP\_3V output pin is intended to be connected to the output enable of a clock generator or buffer chip, so that the clocks to the GX1 and the CS5530A (and most other system devices) can be stopped. The CS5530A continues to decrement all of its internal device timers and respond to external SMI interrupts after the input clock has been stopped, as long as the external 32 KHz clock on pin AE3 [CLK\_32K] continues to oscillate. (Note that the SP4GX10 platform does not include this 32 KHz oscillator. The oscillator must be added in order to support the 3 Volt Suspend mode). Any SMI event or unmasked interrupt pin causes the CS5530A to deassert the SUSP\_3V pin, thereby restarting the system clocks. (See Section 5.1.10 "CS5530A Companion Device Issues" on page 27 for details on how to use interrupts to wakeup the system.) As the CPU or other device might include a PLL, the CS5530A holds SUSP# active for a pre-programmed period of delay (the PLL re-sync delay) that varies from 0 to 15 ms to allow the PLL to resynchronize. After this period has expired, the CS5530A deasserts SUSP#, and the GX1 responds by deasserting SUSPA#, stopping Suspend. SMI# is held active for the entire period, so that the GX1 reenters SMM when the clocks are restarted.

**Note:** The SUSP\_3V pin can be active either high or low. The pin is an input during POR, and is sampled to determine its inactive state. This allows a designer to match the active state of SUSP\_3V to the inactive state for a clock driver output enable by using either a pull-up or a pull-down resistor.

While in the 3 Volt Suspend state the GX1 processor will not respond to anything except the deassertion of SUSP#, as long as SYSCLK has been restarted.

#### 4.1.6.1 Hybrid 3 Volt Suspend States

Since the 3 Volt Suspend state control registers reside in two separate parts, it is possible to create hybrid states by setting the bits in different configurations. If CLK\_STP in the GX1 PM\_CNTRL\_CSTP register is not set, then a 3 Volt Suspend state will still occur, except that the SDRAMs will not be put into a self refresh mode. This implies that the GX1 SYSCLK input may not be stopped, for doing so would cause loss of the SDRAM contents.

#### 4.1.7 Triggering Suspend State

The preceding discussions of Suspend and 3 Volt Suspend have referred to the phrase, "trigger a Suspend state".

Suspend-On-Halt is triggered by writing a HLT command to the GX1 processor. A Suspend state is triggered by writing to one of two CS5530A Function 0 (F0) registers, Index AEh or AFh. Depending on the state of certain register bits, these write commands trigger a Suspend state as described in the methods below. Before using either of these methods, the SUSP#/SUSPA# handshake must be enabled. To enable the handshake, set CS5530A F0 Index 80h[0] = 1.

#### Method 1: F0 Index AEh: Software CPU Suspend Command (Write Only):

If bit 0 in the CS5530A Clock Stop Control Register is set low (F0 Index BCh[0] = 0) and all SMI status bits are 0, a write to this register causes a SUSP#/SUSPA# handshake with the CPU, placing the CPU in a Suspend state. The data written is irrelevant. Once in this state, any unmasked IRQ or SMI releases the CPU Suspend condition.

If F0 Index BCh[0] = 1, writing to this register invokes a 3 Volt Suspend. The SUSP\_3V pin is asserted after the SUSP#/SUSPA# halt. Upon a Resume event (see Note), the PLL delay programmed in the F0 Index BCh[7:4] is invoked, allowing the clock chip and CPU PLL to stabilize before deasserting the SUSP# pin.

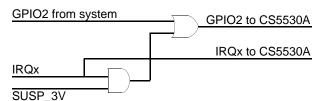

**Note:** If the system clocks are stopped, the external IRQ4, IRQ3, and IRQ1 pins, when enabled (CS5530A F3BAR+Memory Offset 1Ah[4:3]), are the only IRQ pins that can be used as a Resume event. If GPIO2, GPIO1, and GPIO0 are enabled as an external SMI source (CS5530A F0 Index 92h[2:0]), they too can be used as a Resume event. No other CS5530A pins can be used to wakeup the system from Suspend when the clocks are stopped. As long as the 32 KHz clock remains active, internal SMI events are also Resume events.

See Section 5.1.10 "CS5530A Companion Device Issues" on page 27 for details on how to use IRQs and GPIOs to wakeup the system.

#### Method 2: Function 0 Index AFh: Software CPU Stop Clock Suspend (Write Only):

A write to this register causes a SUSP#/SUSPA# handshake with the CPU, placing the CPU in a low-power state. Following this handshake, the SUSP\_3V pin is asserted. The SUSP\_3V pin is intended to be used to stop all system clocks.

Upon a Resume event (see Note), the SUSP\_3V pin is deasserted. After a slight delay, the CS5530A deasserts the SUSP# signal. Once the clocks are stable, the processor deasserts SUSPA# and system operation resumes.

**Note:** If the system clocks are stopped, the external IRQ4, IRQ3, and IRQ1 pins, when enabled (CS5530A F3BAR+Memory Offset 1Ah[4:3]), are the only IRQ pins that can be used as a Resume event. If GPIO2, GPIO1, and GPIO0 are enabled as an external SMI source (CS5530A F0 Index 92h[2:0]), they too can be used as a Resume event. No other CS5530A pins can be used to wakeup the system from Suspend when the clocks are stopped.

See Section 5.1.10 "CS5530A Companion Device Issues" on page 27 for details on how to use IRQs and GPIOs to wakeup the system.

## 4.2 System Platform Power States

The discussion of system power states that follows is generic and may apply to any system platform based on the AMD Geode<sup>™</sup> processor. References to letter-named modes (e.g., Mode C) are to specific states of the AMD's Geode<sup>™</sup> SP4GX10 system platform. These letter-named modes are described in detail in the Section 5.0 on page 12. The terms used in this section: "Off", "Doze", "Standby", and "Suspend", are industry-standard terms and are deliberately used here for persons familiar with power management techniques.

#### 4.2.1 Mechanical Off State

The Mechanical Off state is entered and left by a mechanical means such as turning off an external AC power switch, or disconnecting the power cord or battery. In the Mechanical Off state no electrical current is applied to the circuitry. The OS must be fully restarted to return to the Working state unless a Save-to-Disk or Save-to-RAM operation was performed prior to entering the Mechanical Off state. No hardware context is maintained in the circuitry except for data in the battery backed CMOS RAM (if present). The power consumption in the Mechanical Off state is zero.

#### 4.2.2 Off State

In the Off state the SP4GX10 consumes minimal power. The CPU is powered off and no code is executing. The Off state is entered via hardware or software control. The Off state is entered under hardware control by depressing the on/off switch on the board (a four second hold delay may be required depending upon SuperI/O setup). The Off state can be entered under software control through the appropriate BIOS call or by writing the appropriate SuperI/O register directly. Typically the BIOS abstraction layer is employed.

The system context in the Off state is not maintained so the OS must be fully restarted to return to the Working state unless a Save-to-Disk or Save-to-RAM operation was completed prior to entering the Off state.

Return to the Working state from the Off state is accomplished by activation of the wake inputs. These wake inputs include: activation of the on/off button, PME# activation via Wake-on-LAN, activation of the RI# (ring) input, or activation of the RTC (real-time clock) alarm. Note that all of these wake events assume the presence of the National Semiconductor PC97317 SuperI/O. Return to the Working state from Off requires approximately the same amount of time as a return from the Mechanical Off state. The Off state is the typical Off state of a system.

#### 4.2.3 Working State

In the Working state, the system is operational and user mode (application) threads are executing. In this state, system elements and peripherals may have their power dynamically managed based on system operation. The system design allows the user to select various performance versus power operation modes and profiles. The system responds to external events in real-time. There are several variants of the Working state. Note that the implementation modes (Modes A-I) described in Section 5.1 "Mode Programming" on page 12 represent the implementation on the SP4GX10 system platform. It is expected that there would be some modification of these operational states to fit a specific system design.

#### 4.2.3.1 Full-On Mode

The Full-On mode is the full power operating mode of the system when in the Working state. This mode is the same as Mode A. All devices are fully powered and operating at full speed. All component clocks are present and running at full speed. The Full-On mode is entered upon initial system power up from the Mechanical Off or Off state and is also entered in response to a trigger event from one of several sources if the system is in one of the power conservation modes of the Working State.

When the Full-On mode is entered, the Doze timers are enabled if the system is setup to use Doze mode hardware timers. When the Doze mode timers elapse, the system enters the first level of power conservation.

#### 4.2.3.2 Doze Mode

The Doze mode is the first level of power conservation of the system when in the Working state. The system is in Suspend Modulation (Mode B) or Active Idle (Mode C), depending on the method of entry, when in Doze mode. While operating in Doze mode there is virtually no decrease in end-user perceivable performance of functionality. In Doze mode, power savings is achieved through the use of Suspend Modulation to the GX1 and/or by entering the Suspend-On-Halt state. Both states may be present at the same time. While the primary means of power saving is achieved through the use of Suspend Modulation, the system design may also allow selective, autonomous powering down of non-critical peripherals if they are not accessed. The important consideration is user-observed latency. In Doze mode the latency must be kept to a minimum. There are two methods for entering Doze mode.

The first method of Doze mode entry is under software control through the execution of the HLT instruction. In a simple single threaded application it may be possible to craft the design so as to include the HLT opcode directly within the application executable. In operation, the system will execute to the HLT instruction and remain there until an INTR (Interrupt) or SMI# (System Management Interrupt) is sensed. In a more sophisticated system with multiple threads running, the task manager can include the HLT instruction when the system idle thread is called. Alternatively, the system idle thread can call back to the BIOS with an APM-aware CPU-idle call.

The second method of Doze mode entry occurs when the hardware (such as an event timer) signals a time-out. This event will typically signal through the generation of an SMI. The SMM handler responds by enabling Suspend Modulation. Suspend Modulation effectively reduces the CPU power consumption by asserting and de-asserting the SUSP# input to the GX1. The duty cycle of Suspend Modulation is fully programmable, however, aggressive settings are recommended. The system can be setup to override the Suspend Modulation when critical events such as interrupts (INTR) or system management interrupts (SMI#) must be processed. This override is referred to interrupt speedup and insures low latency when processing critical operations such as mouse movement or keystrokes.

It is important to note that the Suspend Modulation state can also be entered in response to a thermal event. If the system thermal sensor detects that the temperature has risen above an established threshold, a thermal activity SMI is signaled and the SMM handler enables Suspend Modulation in response. When the over-temperature condition is no longer present, the system is returned to the Full-On mode, assuming no further time-outs have occurred.

When Doze mode is entered, the Standby mode timers are enabled. Exit from Doze mode to the Full-On mode occurs upon activation of an interrupt or SMI. If processing of the event does not cause a reload of the Doze mode timer (and therefore the Standby mode timer), then Doze mode is reentered upon completion of the processing of the event. Doze mode can also be exited to the Standby mode if the Standby mode timers elapse or if software commands an entry to the Standby mode.

#### 4.2.3.3 Standby Mode

The Standby mode is the second level of power conservation for the SP4GX10 platform. This mode is the same as Mode D or E depending on the system implementation. Higher user response latency and performance degradation are evident following entry into the Standby state. The Geode devices are in the "CPU Suspend" state. The LCD panel and backlight are disabled but all other peripherals are operational in the implementation of Standby mode on the SP4GX10 platform. It is possible to autonomously, selectively power down additional peripherals in this state using the precepts outlined in the subsections of Section 6.0 "Peripheral Power Management" of this application note. The specific implementation is at the discretion of the system designer. It is important to note that the complexity of the wakeup logic and the system response latency increase if additional devices are powered down in Standby mode, but the power savings may justify the effort.

Standby mode is entered when the appropriate timer elapses and generates an SMI to signal a Standby mode time-out. The SMM handler responds by placing the system into Mode E or F. The mode used is selectable by the system designer. In Mode E the GX1 is in Suspend state and the LCD is disabled. In Mode F, the GX1 is Suspended and the graphics interface is fully disabled.

Significant power savings are realized by placing the GX1 in the CPU Suspend state and disabling the graphics interface. The system still responds to system interrupts and SMIs and processes them without enabling the display. This allows timer ticks and various system management events to be processed while maintaining a reduced power consumption state. The interrupt speedup mechanism (see Section 4.1.5.4 "SMI Speedup Disable" on page 5) is employed in order to process system interrupts while in the Standby mode. User or application generated interrupts such as keystrokes, mouse movements, or disk accesses return the system to the Full-On mode.

When Standby mode is entered, the Suspend mode timers are enabled. Exit from Standby mode to the Full-On mode occurs upon activation of an interrupt or SMI. If processing of the event does not cause a reload of the Standby and Doze mode timers, then Standby is re-entered upon completion of the processing of the event. Standby mode can also be exited to the Suspend mode if the Suspend mode timers elapse or if software commands an entry to the Suspend mode.

#### 4.2.3.4 Suspend Mode

The Suspend mode is the third and the most aggressive power conservation mode. This mode is the same as Mode H or Mode I, depending on the degree to which clock-stopping has been implemented in the hardware. User response latency and performance degradation are evident following entry into the Suspend mode. The GX1 and CS5530A are in the 3 Volt Suspend state. All system peripherals are disabled in this mode, but can be quickly re-enabled and returned to an operational state. Suspend mode results in the highest level of system power conservation while still maintaining the ability to quickly restore the system to the Full-On mode. All peripherals are still powered in this mode, only operation (and possibly clock inputs) is inhibited.

Suspend mode is entered when the appropriate timer elapses and generates an SMI to signal a Suspend mode time-out or when software specifically commands a Suspend mode entry, The SMM handler responds to the SMI by placing the system into Mode G or I. The mode used is selectable by the system designer; detailed design choices must be made to support halting various system clocks. In Mode G the system is suspended but all clocks are maintained. In Mode I, the system is suspended and the external clock inputs to the system are halted. Mode I represents the lowest possible power state while maintaining relatively low latency of return to the Full-On state.

#### 4.2.4 Save-to-Disk/Save-to-RAM

The GX1 and the CS5530A have the capability to save their complete state to either non-volatile (NV) RAM or to disk. Once this information has been saved, the system can be turned off entirely. When powered back on, the system can be returned exactly back to the state it was in when the save process began. This means that the system does not have to be rebooted in the traditional sense.

#### 4.2.4.1 The Saving Medium

The medium to which the information is saved must be non-volatile, meaning, the memory contents must remain unchanged when power is removed and reapplied. Hard or floppy disks are inherently non-volatile; RAM can be made non-volatile by design. A small bank of static RAM could be added to the design, because static RAM does not require refresh cycles and thus would be very low power in the Off state. Dynamic RAM could also be used, provided it can be placed into a self refresh state. In both cases, power must be continuously applied to the RAM, even (especially) when system power is off. Of course, precautions must be taken in the system design to make sure that there is sufficient space on the saving medium to store the state information. The system must contain software specifically written to perform the Save function. It is beyond the scope of this application note to present the design of a system capable of performing Save-to-Disk or Save-to-RAM, including the required software. This note simply points out the special features of the GX1 and CS5530A that enable these functions.

#### 4.2.4.2 Shadow Registers

The CS5530A contains a set of "shadow registers" that facilitate saving certain types of system state information. These registers (see Table 8-4 "Power Management Shadow Registers" for bit descriptions) provide a means to record the status and setup for each standard device in any system;

- DMA Controller

- Programmable Interval Timer (PIT)

- Programmable Interrupt Controller (PIC)

- Real-Time Clock (RTC)

The PC/AT compatible floppy port is not part of the CS5530A. If a floppy is attached on the ISA bus by a SuperI/O or by some other means, some of the FDC registers are shadowed in the CS5530A. The FDC shadow registers should also be saved during the Save-to-RAM or Save-to-Disk operation.

#### 4.2.5 System State Transitions

Designing a system for power management is best done using a state transition diagram. The designer should first identify which power management states the system being designed should support, and then identify what actions should cause transitions between the states.

#### 4.2.5.1 Basic Power Management States

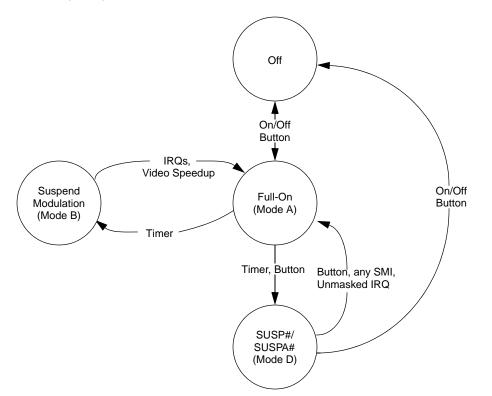

Figure 4-1 illustrates a system with basic power management features. The system has four states, two of them being power management states, and the other two are the basic On and Off states that any system will have.

The system shown will transition to either Suspend Modulation or to Mode D, which is a form of Suspend (see Section 4.1.5 "Suspend Modulation").

#### 4.2.5.2 Advanced Power Management States

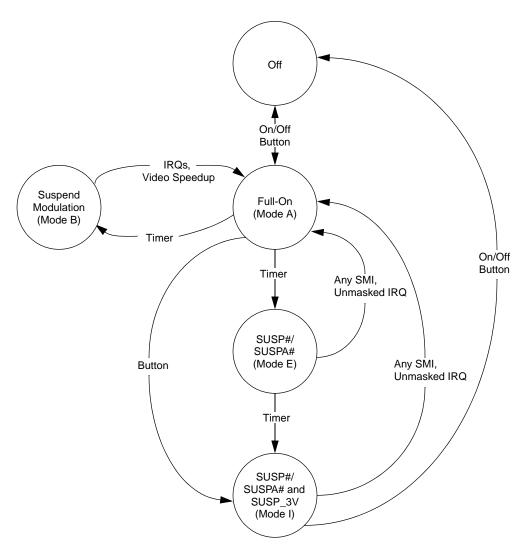

Figure 4-2 on page 11 illustrates a more complex system, whose hardware is configured similar to that shown in Figure 3-1 "Device Interconnections" on page 2. This system supports 3 Volt Suspend (Mode I) in addition to simple Suspend and Suspend Modulation. Note the presence of a button-push to immediately put the system into 3 Volt Suspend.

#### **APM Support**

The GX1 and CS5530A provide APM-compliant power states. The "APM Standby" state is equivalent to the Suspend state. The "APM Suspend" state is equivalent to the 3 Volt Suspend state. The system BIOS (XpressROM) for the SP4GX10 contains an APM-compliant BIOS interface.

It is not the purpose of this discussion to give any details on interfacing to the SP4GX10 XpressROM BIOS, however, a few general comments regarding APM are made.

Some IA systems rely solely on an APM (Advanced Power Management) driver for DOS, Microsoft<sup>®</sup> Windows<sup>®</sup> 95/98, and other operating systems for enabling the operating system to power-manage the CPU. APM provides several services that enhance the system power management by determining when the CPU is idle. For the CPU, APM is theoretically the best approach but there are some drawbacks:

- APM is an OS-specific driver, and may not be available for some operating systems.

- Application support is inconsistent. Some applications in the foreground may prevent Idle calls.

- APM does not help with Suspend determination or peripheral power management.

The CS5530A provides two entry points for APM support:

- Software CPU Suspend control via the CPU Suspend Command Register (F0 Index AEh).

- Software SMI entry via the Software SMI Register (F0 Index D0h). This allows the APM BIOS to be part of the SMI handler.

The bit formats for these registers are shown in Table 8-3 "CS5530A Suspend/Suspend Modulation Configuration Related Registers" on page 38.

Figure 4-1. Basic Power Management State Transitions

Figure 4-2. Advanced Power Management State Transitions

# 5.0 SP4GX10 System Platform Working State Modes

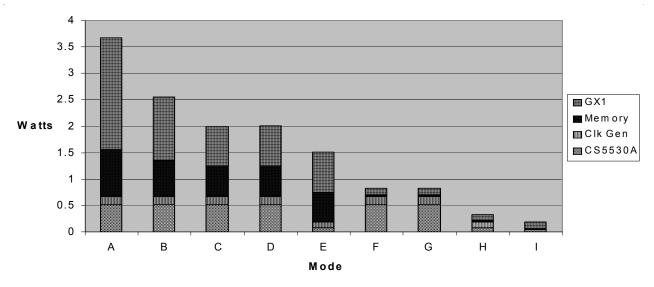

Nine modes for the Working state, labeled A through I, have been defined for the SP4GX10 system platform; however, many additional states are possible when all combinations of peripheral device power states (see Section 6.0 "Peripheral Power Management" on page 30) are considered. Modes A through I describe system-wide effects of power state changes in the Geode devices (the GX1 processor and CS5530A companion) and do not reflect any changes in the power status of peripheral devices.

Modes involving 3 Volt Suspend require that a 32 KHz oscillator be added to the SP4GX10 board; these are modes F through I inclusive.

The modes are:

- Mode A: Full-On.

- Mode B: Suspend Modulation.

- Mode C: Suspend-on-Halt (Active Idle).

- Mode D: SUSP#/SUSPA#.

- Mode E: SUSP#/SUSPA# with some clock stopped (using PM PAL).

- Mode F: SUSP#/SUSPA# with the PM\_CNTRL\_CSTP register set in the GX1 for 3 Volt Suspend (GX\_BASE+Memory Offset 8508h[0] = 1).

- Mode G: SUSP#/SUSPA# and SUSP\_3V active with all clocks still running.

- Mode H: SUSP#/SUSPA# and SUSP\_3V active with some PCI clocks stopped.

- Mode I: SUSP#/SUSPA# and SUSP\_3V active with all clocks stopped.

## 5.1 Mode Programming

The following discussion provides details of each of the defined Modes A through I. Each mode is briefly discussed and the GX1/CS5530A register setups are provided.

#### 5.1.1 Mode A: Full-On

This is the fully on and normal state. All power planes are on and all clocks are running.

#### 5.1.2 Mode B: Suspend Modulation

This is the first level of power management, and must have a very quick response latency so that it can be entered very quickly. The GX1 processor enters Suspend Modulation if there is no activity after a certain amount of time. Any interrupt and/or SMI causes the system to exit from this state.

- Mode B device status:

- GX1: Suspend Modulation

- CS5530A: Suspend Modulation

- Main memory: Active

- Other devices: Active

- Mode B entry event:

- Timer expiration (e.g., CS5530A GP Timer 1)

- Thermal activity (if applicable)

- Mode B exit event:

- Any unmasked Interrupts

- Any asserted SMI

- NMI

- Accessing the video port

- Video activity (any access to the VGA register space, the VGA frame buffer, the graphic accelerator control register and the configured graphic frame buffer)

Table 5-1 provides the required register programming for Mode B.

| Register                       | Setting   | Description                                                                                                        |

|--------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------|

| GX1 Processor                  |           |                                                                                                                    |

| Index C2h (CCR2)               | Bit 7 = 1 | Suspend Pins (SUSP# and SUSPA#) (1 = Enable)                                                                       |

|                                | Bit 3 = 0 | Suspend-on-Halt                                                                                                    |

| Index 3Ch (CCR3)               | Bit 3 = 1 | Allow Suspend in SMM Mode (1 = SUSP# recognized in SMM mode)                                                       |

| GX_BASE+Memory<br>Offset 8508h | Bit 0 = 0 | Clock Stop (0 = Suspend Refresh Mode): Core stopped, the clocks to the memory and display controller remain active |

| CS5530A Companion Device       |           |                                                                                                                    |

## Table 5-1. Mode B Register Programming

| Register                   | Setting                   | Description                                                                        |

|----------------------------|---------------------------|------------------------------------------------------------------------------------|

| F0 Index 80h               | Bit 4 = 1                 | Video Speedup (1 = Enable)                                                         |

|                            | Bit 3 = 1                 | IRQ Speedup (1 = Enable)                                                           |

|                            | Bit 0 = 1                 | Global Power Management (1 = Enable)                                               |

| F0 Index 88h               | See Footnote <sup>1</sup> | GP Timer 1 Count                                                                   |

| F0 Index 89h               | GPT1 Control              |                                                                                    |

|                            | Bit 7 = 1                 | Timebase (1 = 1 ms)                                                                |

|                            | Bit 6 = 0                 | Re-trigger on UDEF3 (0 = Disable)                                                  |

|                            | Bit 5 = 0                 | Re-trigger on UDEF2 (0 = Disable)                                                  |

|                            | Bit 4 = 0                 | Re-trigger on UDEF1 (0 = Disable)                                                  |

|                            | Bit 3 = 1                 | Re-trigger on Keyboard/Mouse (1 = Enable)                                          |

|                            | Bit 2 = 1                 | Re-trigger on Parallel/Serial (1 = Enable)                                         |

|                            | Bit 1 = 1                 | Re-trigger on Floppy (1 = Enable)                                                  |

|                            | Bit 0 = 1                 | Re-trigger on Primary HDD (1 = Enable)                                             |

| F0 Index 8Ah               | 00h                       | GP Timer 2 Count                                                                   |

| F0 Index 8Bh GPT2 Contr    |                           |                                                                                    |

|                            | Bit 7 = 0                 | Re-trigger on Secondary HDD (0 = Disable)                                          |

|                            | Bit 6 = 0                 | VGA Timer Base (0 = 1 ms)                                                          |

|                            | Bit 5 = 0                 | GPT2 shift (0 = No shift)                                                          |

|                            | Bit 4 = 0                 | GPT1 shift (0 = No shift)                                                          |

|                            | Bit 3 = 1                 | Timebase for GPT2 (1 = 1 ms)                                                       |

|                            | Bit 2 = 0                 | Re-trigger on GPT2 (0 = Disable)                                                   |

|                            | Bits [1:0] = 00           | Reserved                                                                           |

| F0 Index 8Ch               | See Description<br>Column | IRQ Speedup Timer Count (timer load value): 1 ms,<br>a typical value = 2 to 4 ms   |

| F0 Index 8Dh               | See Description<br>Column | Video Speedup Timer Count (timer load value): 1 ms,<br>a typical value = 2 to 4 ms |

| F0 Index 94h               | See Description<br>Column | Suspend Signal Deasserted Count (8-bit counter): 32 µs                             |

| F0 Index 95h               | See Description<br>Column | Suspend Signal Asserted Count (8-bit counter): 32 µs                               |

| F0 Index 96h               | Bit 1 = 1                 | Disable Suspend Modulation when an SMI occurs (1 = Yes)                            |

|                            | Bit 0 = 1                 | Suspend Modulation (1 = Enable)                                                    |

| F1BAR+Memory<br>Offset 08h | Any Value                 | Read to re-enable Suspend Modulation at every SMI exit point                       |

1. The values for GPT1 and GPT2 are selected by the system designer. This value should be the maximum length of time (in either seconds or milliseconds, depending on the counter's timebase) that any device in the re-trigger list may remain inactive before a power management state is triggered.

#### 5.1.3 Mode C: Suspend-on-Halt Instruction

This is the second level of power management. The GX1 enters this mode if a HLT (Halt) instruction is executed. The SUSPA# pin is active while in this state without asserting of SUSP#.

When entered, Suspend-on-Halt stops the clocks to the processor core while the integrated functions (graphics, memory controller, PCI controller) are still active.

- Mode C device status:

- GX1: Active Idle

- CS5530A: Active

- Main memory: Active

- Other devices: Active

- Mode C entry event:

- APM call

- Execute a HLT instruction

- Mode C exit event:

- Any unmasked Interrupts

- Any asserted SMI

- NMI

- Accessing the video port

- Video activity (any access to the VGA register space, the VGA frame buffer, the graphic accelerator control register and the configured graphic frame buffer)

Table 5-2 provides the required register programming for Mode C.

| Register                       | egister Setting Description |                                                                                                                    |

|--------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------|

| GX1 Processor                  |                             | ·                                                                                                                  |

| Index C2h (CCR2)               | Bit 7 = 1                   | Suspend Pins (SUSP# and SUSPA#) (1 = Enable)                                                                       |

|                                | Bit 3 = 1                   | Suspend-on-Halt (1 = Enable)                                                                                       |

| GX_BASE+Memory<br>Offset 8508h | Bit 0 = 0                   | Clock Stop (0 = Suspend Refresh Mode): Core stopped, the clocks to the memory and display controller remain active |

#### Table 5-2. Mode C Register Programming

#### 5.1.4 Mode D: SUSP#/SUSPA#

The GX1 enters this mode if the GP Timer 1 in the CS5530A expires. Upon expiration, the BIOS writes the CS5530A CPU Suspend Command register (F0 Index AEh) to cause a SUSP#/SUSPA# handshake. The SUSP# pin is asserted by the CS5530A and the GX1 responds by asserting the SUSPA# pin to indicate that the processor has entered Suspend. If USB is enabled, the SUSPA# signal is deasserted every 1 ms due to the 1 ms REQ1# signal from the CS5530A (USB controller).

SUSP#/SUSPA is similar to Suspend-on-Halt except for its entry and exit method in terms of hardware protocol.

- Mode D device status:

- GX1: Suspend

- CS5530A: Suspend

- Main memory: Active

- Other devices: Active

- Mode D entry event:

- Expiration of GP Timer 1

- Mode D exit event:

- Any unmasked interrupts (e.g., keyboard or mouse activity)

- Any asserted SMI

- NMI

- Accessing the video port

- Video activity (any access to the VGA register space, the VGA frame buffer, the graphic accelerator control register and the configured graphic frame buffer)

Table 5-3 on page 15 provides the required register programming for Mode D.

| (SUSP# and SUSPA#) (1 = Enable)<br>alt> Don't care<br>= Suspend Refresh Mode): Core stopped, the clocks to the<br>isplay controller remain active<br>Management (1 = Enable)<br>(0 = Disable) |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| alt> Don't care<br>= Suspend Refresh Mode): Core stopped, the clocks to the<br>isplay controller remain active<br>Management (1 = Enable)<br>(0 = Disable)                                    |

| = Suspend Refresh Mode): Core stopped, the clocks to the<br>isplay controller remain active<br>Management (1 = Enable)<br>(0 = Disable)                                                       |

| isplay controller remain active<br>Management (1 = Enable)<br>(0 = Disable)                                                                                                                   |

| (0 = Disable)                                                                                                                                                                                 |

| (0 = Disable)                                                                                                                                                                                 |

|                                                                                                                                                                                               |

|                                                                                                                                                                                               |

|                                                                                                                                                                                               |

| isable)                                                                                                                                                                                       |

| isable)                                                                                                                                                                                       |

| isable)                                                                                                                                                                                       |

| se (0 = Disable)                                                                                                                                                                              |

| (0 = Disable)                                                                                                                                                                                 |

| sable)                                                                                                                                                                                        |

| (0 = Disable)                                                                                                                                                                                 |

| bunt                                                                                                                                                                                          |

|                                                                                                                                                                                               |

| 1 ms)                                                                                                                                                                                         |

| JDEF3 (0 = Disable)                                                                                                                                                                           |

| JDEF2 (0 = Disable)                                                                                                                                                                           |

| JDEF1 (0 = Disable)                                                                                                                                                                           |

| Keyboard/Mouse (1 = Enable)                                                                                                                                                                   |

|                                                                                                                                                                                               |

| Parallel/Serial (1 = Enable)                                                                                                                                                                  |

| Parallel/Serial (1 = Enable)<br>Floppy (1 = Enable)                                                                                                                                           |

| ι                                                                                                                                                                                             |

#### Table 5-3. Mode D Register Programming

| Register     | Setting                   | Description                                                                        |

|--------------|---------------------------|------------------------------------------------------------------------------------|

| F0 Index 8Ah | 00h                       | GP Timer 2 Count                                                                   |

| F0 Index 8Bh | GPT2 Control              |                                                                                    |

|              | Bit 7 = 0                 | Re-trigger on Secondary HDD (0 = Disable)                                          |

|              | Bit 6 = 0                 | VGA Timer Base (0 = 1 ms)                                                          |

|              | Bit 5 = 0                 | GPT2 shift (0 = No shift)                                                          |

|              | Bit 4 = 0                 | GPT1 shift (0 = No shift)                                                          |

|              | Bit 3 = 1                 | Timebase for GPT2 (1 = 1 ms)                                                       |

|              | Bit 2 = 0                 | Re-trigger on GPT2 (0 = Disable)                                                   |

|              | Bits [1:0] = 00           | Reserved                                                                           |

| F0 Index 8Ch | See Description<br>Column | IRQ Speedup Timer Count (timer load value): 1 ms,<br>a typical value = 2 to 4 ms   |

| F0 Index 8Dh | See Description<br>Column | Video Speedup Timer Count (timer load value): 1 ms,<br>a typical value = 2 to 4 ms |

| F0 Index 94h | See Description<br>Column | Suspend Signal Deasserted Count (8-bit counter): 32 µs                             |

| F0 Index 95h | See Description<br>Column | Suspend Signal Asserted Count (8-bit counter): 32 µs                               |

| F0 Index AEh | Any Value                 | S/W CPU Suspend Command                                                            |

| F0 Index BCh | Bit 0 = 0                 | CPU Clock Stop (0 = Normal operation)                                              |

| Table 5-3. | Mode D R | egister Proc  | aramming (  | (Continued) |

|------------|----------|---------------|-------------|-------------|

|            | mode D N | cylater i rog | ji anning y | (Commuca)   |

1. The values for GPT1 and GPT2 are selected by the system designer. This value should be the maximum length of time (in either seconds or milliseconds, depending on the counter's timebase) that any device in the re-trigger list may remain inactive before a power management state is triggered.

#### 5.1.5 Mode E: SUSP#/SUSPA# with Some PCI Clocks Stopped (Using the PM PAL)

Mode E is similar to Mode D (i.e., SUSP#/SUSPA) except the clocks to the PCI slots and the National Semiconductor DP83815 MacPHYTER are stopped. The PAL asserts the signal clocks to the clock generator to stop some PCI clocks when: SUSPA# is low, PCIRST# is high, SUSP\_3V is high, audio is inactive, USB is inactive, INTR is low, SMI# is high, and wakeup events are inactive. If USB is enabled, the SUSPA# signal is deasserted every 1 ms due to the 1 ms REQ1# signal from the CS5530A (USB controller).

- Mode E device status:

- GX1: Suspend

- CS5530A: Suspend

- Main memory: Active

- PCI slots: Clocks stopped

- DP83815: Inactive

- Other devices: Active

- Mode E entry event:

Expiration of the GP Timer 1 and PAL equation

- Mode E exit event:

- Any unmasked Interrupts (e.g., keyboard or mouse activity).

- Any asserted SMI

- NMI

- PME# from DP83815

- PME# from PCI slots

- Accessing the video port

- Video activity (any access to the VGA register space, the VGA frame buffer, the graphic accelerator control register and the configured graphic frame buffer)

- See Section 5.1.10 "CS5530A Companion Device Issues" on page 27 for information on interrupt wakeups.

Table 5-4 provides the required register programming for Mode E.

| Table 5-4. | Mode E R | Reaister P | rogramming |

|------------|----------|------------|------------|

|            |          | egiotoi i  |            |

| Register                       | Setting                   | Description                                                                                                        |

|--------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------|

| GX1 Processor                  |                           |                                                                                                                    |

| Index C2h (CCR2) Bit 7 = 1     |                           | Suspend Pins (SUSP# and SUSPA#) (1 = Enable)                                                                       |

|                                | Bit 3 = X                 | Suspend-on-Halt> Don't care                                                                                        |

| GX_BASE+Memory<br>Offset 8508h | Bit 0 = 0                 | Clock Stop (0 = Suspend Refresh Mode): Core stopped, the clocks to the memory and display controller remain active |

| CS5530A Companion              | Device                    |                                                                                                                    |

| F0 Index 80h                   | Bit 0 = 1                 | Global Power Management (1 = Enable)                                                                               |

| F0 Index 81h Idle Timer Enable |                           |                                                                                                                    |

|                                | Bit 7 = 0                 | Video access (0 = Disable)                                                                                         |

|                                | Bit 6 = 0                 | UDEF3 (0 = Disable)                                                                                                |

|                                | Bit 5 = 0                 | UDEF2 (0 = Disable)                                                                                                |

|                                | Bit 4 = 0                 | UDEF1 (0 = Disable)                                                                                                |

|                                | Bit 3 = 0                 | Keyboard/Mouse (0 = Disable)                                                                                       |

|                                | Bit 2 = 0                 | Parallel/Serial (0 = Disable)                                                                                      |

|                                | Bit 1 = 0                 | Floppy (0 = Disable)                                                                                               |

|                                | Bit 0 = 0                 | Primary HDD (0 = Disable)                                                                                          |

| F0 Index 88h                   | See Footnote <sup>1</sup> | GP Timer 1 Count                                                                                                   |

| Register     | Setting                   | Description                                                                        |

|--------------|---------------------------|------------------------------------------------------------------------------------|

| F0 Index 89h | GPT1 Control              |                                                                                    |

|              | Bit 7 = 1                 | Timebase (1 = 1 sec)                                                               |

|              | Bit 6 = 0                 | Re-trigger on UDEF3 (0 = Disable)                                                  |

|              | Bit 5 = 0                 | Re-trigger on UDEF2 (0 = Disable)                                                  |

|              | Bit 4 = 0                 | Re-trigger on UDEF1 (0 = Disable)                                                  |

|              | Bit 3 = 1                 | Re-trigger on Keyboard/Mouse (1 = Enable)                                          |

|              | Bit 2 = 1                 | Re-trigger on Parallel/Serial (1 = Enable)                                         |

|              | Bit 1 = 1                 | Re-trigger on Floppy (1 = Enable)                                                  |

|              | Bit 0 = 1                 | Re-trigger on Primary HDD (1 = Enable)                                             |

| F0 Index 8Ah | 00h                       | GP Timer 2 Count                                                                   |

| F0 Index 8Bh | GPT2 Control              |                                                                                    |

|              | Bit 7 = 0                 | Re-trigger on Secondary HDD (0 = Disable)                                          |

|              | Bit 6 = 0                 | VGA Timer Base (0 = 1 ms)                                                          |

|              | Bit 5 = 0                 | GPT2 shift (0 = No shift)                                                          |

|              | Bit 4 = 0                 | GPT1 shift (0 = No shift)                                                          |

|              | Bit 3 = 1                 | Timebase for GPT2 (1 = 1 ms)                                                       |

|              | Bit 2 = 0                 | Re-trigger on GPT2 (0 = Disable)                                                   |

|              | Bits [1:0] = 00           | Reserved                                                                           |

| F0 Index 8Ch | See Description<br>Column | IRQ Speedup Timer Count (timer load value): 1 ms, a typical value = 2 to 4 ms      |

| F0 Index 8Dh | See Description<br>Column | Video Speedup Timer Count (timer load value): 1 ms,<br>a typical value = 2 to 4 ms |

| F0 Index 94h | See Description<br>Column | Suspend Signal Deasserted Count (8-bit counter): 32 µs                             |

| F0 Index 95h | See Description<br>Column | Suspend Signal Asserted Count (8-bit counter): 32 µs                               |

| F0 Index AEh | Any Value                 | S/W CPU Suspend Command                                                            |

| F0 Index BCh | Bit 0 = 0                 | CPU Clock Stop (0 = Normal operation)                                              |

| Table 5-4. Mode E Register Programming (Continued |

|---------------------------------------------------|

|---------------------------------------------------|

1. The values for GPT1 and GPT2 are selected by the system designer. This value should be the maximum length of time (in either seconds or milliseconds, depending on the counter's timebase) that any device in the re-trigger list may remain inactive before a power management state is triggered.

#### 5.1.6 Mode F: SUSP#/SUSPA# with GX1 Processor SUSP3V Register Set

This mode is the same as SUSP#/SUSPA# except all internal clocks of the GX1 are stopped (set GX\_BASE+Memory Offset 8508h[0] = 1). If USB is enabled, the SUSPA# signal is deasserted every 1 ms due to the 1 ms REQ1# signal from the CS5530A (USB controller).

- Mode F device status:

- GX1: Standby

- CS5530A: Suspend

- Main memory: Self refresh

- Other devices: Active

- Mode F entry event:

- Expiration of CS5530A GP Timer 1

- Mode F exit event:

- Any unmasked interrupts (e.g., keyboard or mouse activity)

- Any asserted SMI

- NMI

- PME# from DP83815

- PME# from PCI slots

- Accessing the video port

- Video activity (any access to the VGA register space, the VGA frame buffer, the graphic accelerator control register and the configured graphic frame buffer)

Table 5-5 provides the required register programming for Mode F.

#### 5.1.6.1 Mode F: SP4GX10 Required Circuit Modification

A hardware modification is required to allow the CS5530A to come out of 3 Volt Suspend:

• A 32.726 KHz OSC must be connected to the 32K input pin (AE3) of CS5530A. Set register F0 Index 44h[5:4] = 10 (CLK\_32K is an input) and tie the oscillator power to  $V_{CC3V}$ .

| Register                       | Setting                                        | Description                                                             |

|--------------------------------|------------------------------------------------|-------------------------------------------------------------------------|

| GX1 Processor                  |                                                |                                                                         |

| Index C2h (CCR2)               | Bit 7 = 1                                      | Suspend Pins (SUSP# and SUSPA#) (1 = Enable)                            |

|                                | Bit 3 = X                                      | Suspend-on-Halt> Don't care                                             |

| GX_BASE+Memory<br>Offset 8508h | Bit 0 = 1                                      | Clock Stop (1 = 3 Volt Suspend Mode): The external clock may be stopped |

| CS5530A Companion              | Device                                         |                                                                         |

| F0 Index 80h                   | Bit 0 = 1 Global Power Management (1 = Enable) |                                                                         |

| F0 Index 81h                   | Idle Timer Enable                              |                                                                         |

|                                | Bit 7 = 0                                      | Video access (0 = Disable)                                              |

|                                | Bit 6 = 0                                      | UDEF3 (0 = Disable)                                                     |

|                                | Bit 5 = 0                                      | UDEF2 (0 = Disable)                                                     |

|                                | Bit 4 = 0                                      | UDEF1 (0 = Disable)                                                     |

|                                | Bit 3 = 0                                      | Keyboard/Mouse (0 = Disable)                                            |

|                                | Bit 2 = 0                                      | Parallel/Serial (0 = Disable)                                           |

|                                | Bit 1 = 0                                      | Floppy (0 = Disable)                                                    |

|                                | Bit 0 = 0                                      | Primary HDD (0 = Disable)                                               |

| F0 Index 88h                   | See Footnote <sup>1</sup>                      | GP Timer 1 Count                                                        |

### Table 5-5. Mode F Register Programming

| Register     | Setting                   | Description                                                                        |

|--------------|---------------------------|------------------------------------------------------------------------------------|

| F0 Index 89h | GPT1 Control              |                                                                                    |

|              | Bit 7 = 1                 | Timebase (1 = 1 sec)                                                               |

|              | Bit 6 = 0                 | Re-trigger on UDEF3 (0 = Disable)                                                  |

|              | Bit 5 = 0                 | Re-trigger on UDEF2 (0 = Disable)                                                  |

|              | Bit 4 = 0                 | Re-trigger on UDEF1 (0 = Disable)                                                  |

|              | Bit 3 = 1                 | Re-trigger on Keyboard/Mouse (1 = Enable)                                          |

|              | Bit 2 = 1                 | Re-trigger on Parallel/Serial (1 = Enable)                                         |

|              | Bit 1 = 1                 | Re-trigger on Floppy (1= Enable)                                                   |

|              | Bit 0 = 1                 | Re-trigger on Primary HDD (1 = Enable)                                             |

| F0 Index 8Ah | 00h                       | GP Timer 2 Count                                                                   |

| F0 Index 8Bh | GPT2 Control              |                                                                                    |

|              | Bit 7 = 0                 | Re-trigger on Secondary HDD (0 = Disable)                                          |

|              | Bit 6 = 0                 | VGA Timer Base (0 = 1 ms)                                                          |

|              | Bit 5 = 0                 | GPT2 shift (0 = No shift)                                                          |

|              | Bit 4 = 0                 | GPT1 shift (0 = No shift)                                                          |

|              | Bit 3 = 1                 | Timebase for GPT2 (1 = 1 ms)                                                       |

|              | Bit 2 = 0                 | Re-trigger on GPT2 (0 = Disable)                                                   |

|              | Bits [1:0] = 00           | Reserved                                                                           |

| F0 Index 8Ch | See Description<br>Column | IRQ Speedup Timer Count (timer load value): 1 ms,<br>a typical value = 2 to 4 ms   |

| F0 Index 8Dh | See Description<br>Column | Video Speedup Timer Count (timer load value): 1 ms,<br>a typical value = 2 to 4 ms |

| F0 Index 94h | See Description<br>Column | Suspend Signal Deasserted Count (8-bit counter): 32 µs                             |