# **HTX<sup>™</sup> - PCI Express Compared**

#### How and Why HyperTransport HTX Proves Best Choice for Compute-Intensive Applications

www.hypertransport.org

Copyright 2008 HyperTransport Consortium

# **HTX<sup>™</sup> Delivers the Extra Performance that** PCI-Class Interconnects Cannot Deliver

Compute-Intensive Applications Expect Best Architectural and Transactional Efficiency from Interconnect Technologies

# HTX

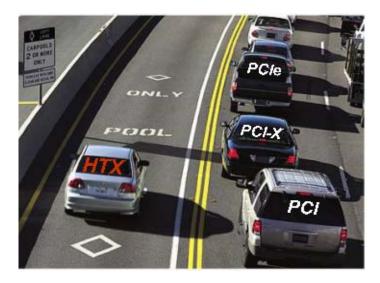

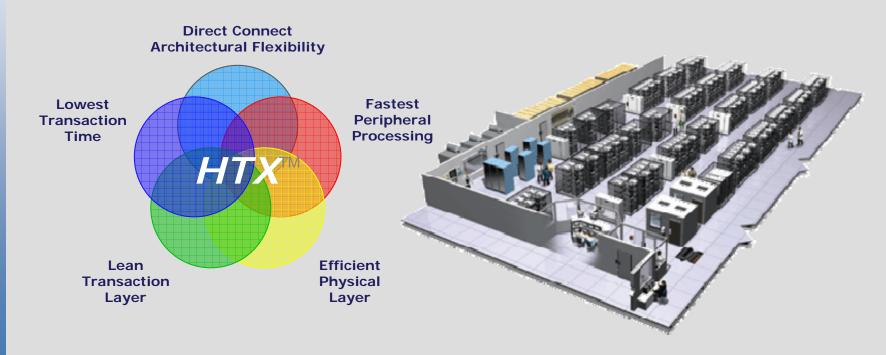

Best-in-Class Slot Connector Interfaces such as HTX and HTX3 are Designed for Lowest Latency, Highest Bandwidth. They are Best Choice for Compute-Intensive Processing and Coprocessing Applications

General Purpose Slot Connector Interfaces such as PCI Express are Designed for Wide End-User Configurability and are Best Choice for Latency-Insensitive Peripheral and I/O Applications

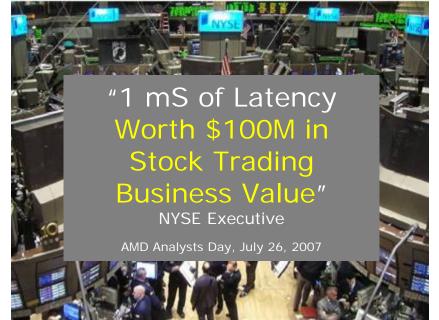

# Latency is The HPC Market Driver

Peak computing power is no longer the metric to consider

Feeding processing units with data is the real concern, and flow control dependencies in applications make latency the key performance metric

Prof. Jose Duato Polytechnic Univ. of Valencia, Spain (\*)

## HTX Has Been and Continues to Be The Lowest Latency Slot Interface in Industry

(\*) Jose Duato is Professor of Computer Science at the Polytechnic University of Valencia, Spain and a world authority in high performance computing (HPC). Prof. Duato has directly contributed to some of the computer industry's most advanced HPC product developments by companies like Compaq, Cray, IBM and Sun Microsystems. In 2006 Prof. Duato received Spain's most prestigious technology achievement award from Queen Sophia of Spain. Dr. Duato is an active contributor to Hypertransport technology and the HyperTransport Consortium.

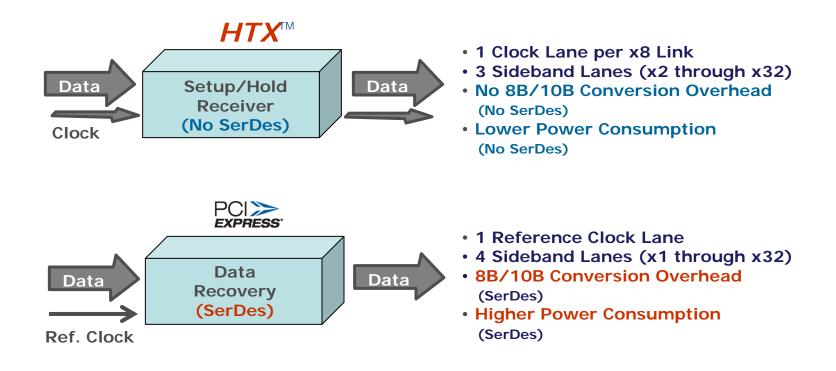

# Multiple Latency Advantages Advantage 1: Physical Layer Efficiency

#### HTX Offers 20% Better Physical Layer Bandwith and Latency

# Multiple Latency Advantages Advantage 2: Leaner Protocol

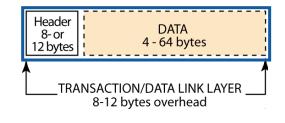

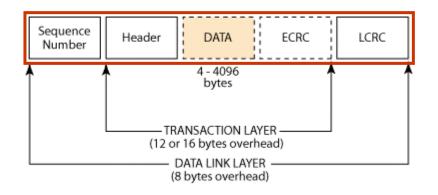

#### **High-Performance Protocol**

- Minimized Packet Overhead

8/12 bytes (Min/Max)

- Ideal for HPC Applications

#### **General Purpose Protocol**

- Considerable Packet Overhead

20/24 bytes (Min/Max)

- Non-Optimal for HPC Applications

HTX's Vastly Leaner Packet Payload Yields Latency Advantage that Scales Linearly with Applications and Job Transactions

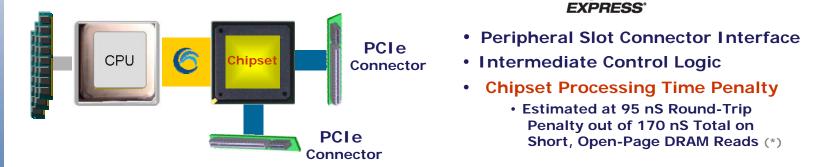

# Multiple Latency Advantages Advantage 3: No Intermediate Logic Overhead

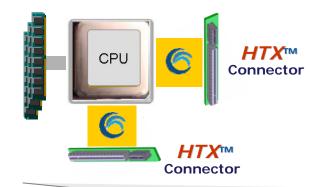

# HTX

- Direct CPU-to-Subsystem Connection

- No Latency Penalty from Intermediate Control Logic

HTX Delivers 55% Lower Latency per Transaction Due to Absence of Intermediate Control Logic and Multiplexing

(\*) PCIe Gen2

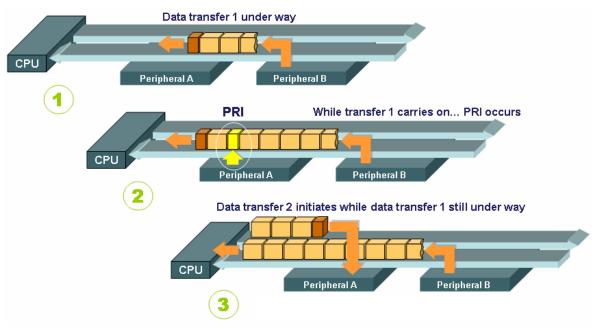

# Multiple Latency Advantages Advantage 4: Peripheral Processing Efficiency

HyperTransport is the Only Interconnect that Can Dynamically Insert Peripheral Read Requests in the Middle of Data Packets (Priority Request Interleaving™)

- PRI's Delivers an Average of 20nS Less Per-Transaction Latency in Heavily Loaded Environments

- High Priority Packets Not Penalized by Low Priority Packets

- Lowest Peripheral Processing Latency

# *HTX*<sup>™</sup> & PCI Express Bandwidth Comparison

| Feature                             | PCIe<br>Gen1 | PCI e<br>Gen2 | HTX          | HTX3          |

|-------------------------------------|--------------|---------------|--------------|---------------|

| Max Clock Rate                      | 2.5 GHz      | 5.0 GHz       | 800 MHz      | 2.6 GHz       |

| Double Data Rate                    | NO           | NO            | YES          | YES           |

| Max Bandwidth x Lane                | 2.5 Gbps     | 5.0 Gbps      | 1.6 GT/s (*) | 5.2 GT/s (*)  |

| 8B/10B Penalty                      | -20%         | -20%          | No Penalty   | No Penalty    |

| Net Bandwidth x Lane                | 2.0 Gbps     | 4.0 Gbps      | 1.6 GT/s (*) | 5.2 GT/s (*)  |

| Net Bandwidth<br>16-Bit - Aggregate | 8 Gbytes/s   | 16 Gbytes/s   | 6.4 GBytes/s | 20.8 GBytes/s |

(\*) HyperTransport supports Double Data Rate (DDR), transferring data on both the leading and trailing edge of the clock. Therefore HyperTransport's bandwidth is more appropriately represented by the term "Transfers/second" than the term "Bits/second"

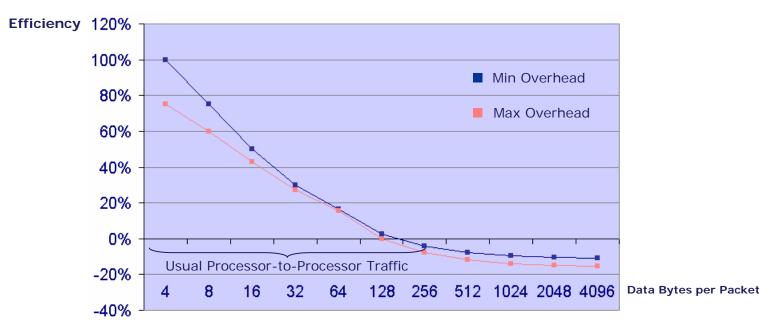

## **HTX**<sup>™</sup> Packet Efficiency in Figures

HTX Delivers up to Twice the Packet Efficiency of PCIe with Proportional Latency Advantages

www.hypertransport.org

Copyright 2008 HyperTransport Consortium

9

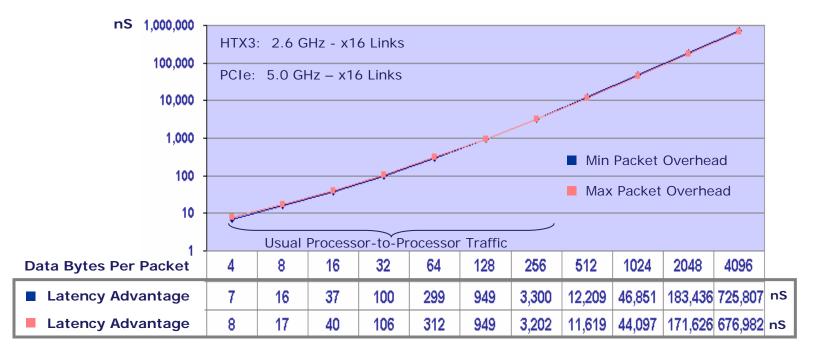

## *HTX*<sup>TM</sup> Per-Packet Latency Advantage

### **HTX3<sup>™</sup> Per-Packet Latency Advantage over PCIe Gen2**

The results take into account PCIe's 20% clock recovery, packet payload and 55% chipset overhead penalties. HTX's Priority Request Interleaving, if applicable, will add to HTX's total latency advantage

# *HTX*<sup>™</sup> Real World Time-to-Result Savings Combined Bandwidth, Pysical Layer and Protocol Latency Advantages

Compute-Intensive Tasks Require Hundreds of Thousand to Billions of Packet Transactions

| Number of Packets Trasferred | 100,000  | 1 Million | 1 Billion |

|------------------------------|----------|-----------|-----------|

| Bytes per Packet Transferred | Per Task | Per Task  | Per Task  |

| 4                            | 0.78 mS  | 7.8 mS    | 7.8 Sec   |

| 16                           | 4 mS     | 40 mS     | 40 Sec    |

| 256                          | 0.32 Sec | 3.20 Sec  | 53 Min    |

| 512                          | 1.16 Sec | 11.62 Sec | 3.23 Hrs  |

#### **HTX3<sup>™</sup> Time-to-Result Saving vs. PCIe Gen2**

The results take into account PCIe's 20% clock recovery, packet payload and 55% chipset overhead penalties. HTX's Priority Request Interleaving<sup>™</sup>, if applicable, will add to HTX's total time-to-result latency advantage

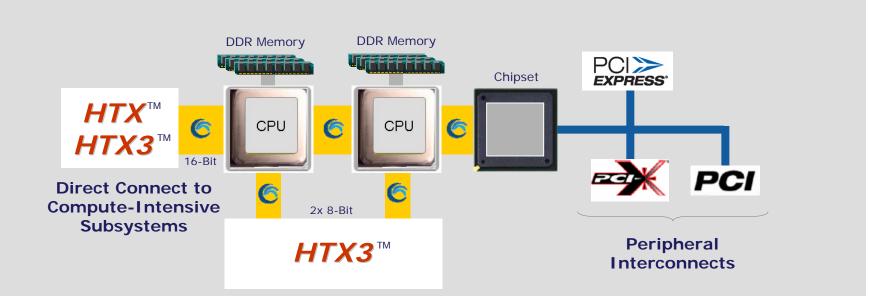

# **HTX3<sup>™</sup> Link Splitting Capability**

The 16-Bit HyperTransport Link in an HTX3 Connector Can Split into Two Independent 8-Bit Links

Allows HTX Subsystem to Connect Directly to 2 CPUs Supports New-Generation System Functionality

www.hypertransport.org

Copyright 2008 HyperTransport Consortium

# *HTX*<sup>™</sup> in Summary

www.hypertransport.org

Copyright 2008 HyperTransport Consortium

13

# **Unique Technical Values**

# HTX<sup>™</sup> Provides Superior Performance and Architectural Capabilities In Line with HPC Market Expectations

# **HTX**<sup>M</sup> Complements PCI Express

With its Unique Architectural and Performance Edge over General Purpose Interconnects, HTX is an Ideal Complement to PCI-Class Slot Connector Interfaces

# **HTX<sup>™</sup> Business Values**

## **HTX<sup>™</sup>** is a Competitive Differentiator for High-Performance Total Solution Vendors

- Negligible BOM Cost

- Leverages PCIe Economy of Scale

- System Flexibility

- Single MB Serves Multiple Markets

- Growing HTX Subsystem Portfolio

- Coprocessors, Accelerated 10GE, ccNUMA Cluster Controllers, Content Processors, Others Released Soon

- Up-Selling Enabler

- Delivers Greater End-User Value

www.hypertransport.org

Copyright 2008 HyperTransport Consortium