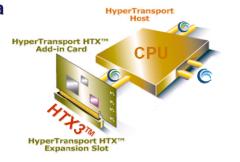

# HyperTransport™ HTX™ Snapshot

#### **HTX<sup>™</sup> Leaps Forward to HTX3<sup>™</sup>**

# **Technology Overview**

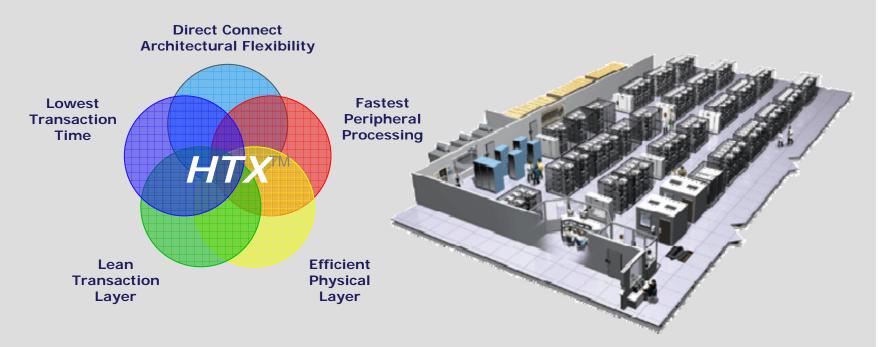

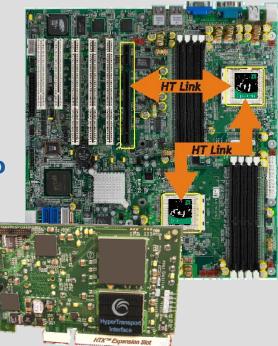

### **HTX<sup>™</sup> Interface = Performance Edge** That PCI-Class Interconnects Cannot Deliver

- Lowest Latency, Highest Bandwidth Direct

Connect Between CPU and Compute-Intensive Subsystems

- Removes Performance Bottlenecks in HPC Data

Processing and Coprocessing Functions

- No Intermediate CPU-to-Subsystem Control Logic

- Reduces Overall Power Consumption

- Complements PCI-Class Interconnects

- Typically Co-Exist with PCI-X and PCI Express Connectors in Same MB Design

#### **Features**

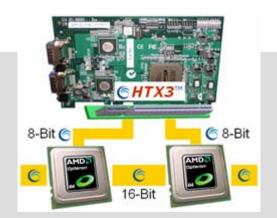

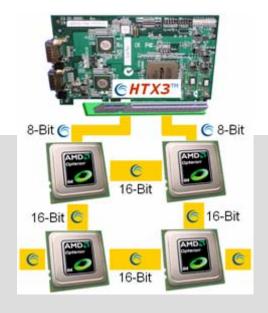

8-Bit and 16-Bit HyperTransport Link Support800 MHz Max Clock Rate6.4 GB/s Bandwidth (16-bit, Aggregate)

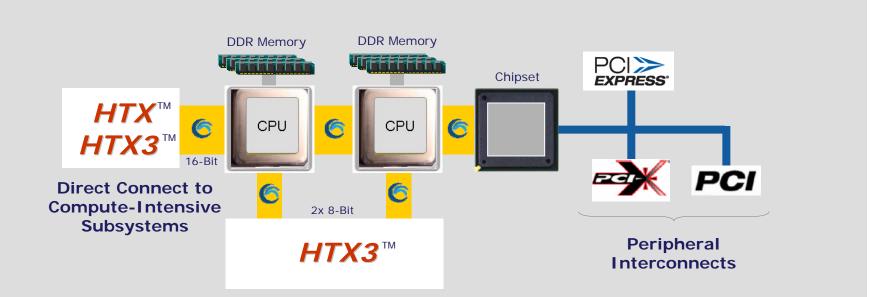

# Introducing HyperTransport<sup>™</sup> *HTX3*<sup>™</sup>

- >3x Bandwidth of Standard HTX Specification

- Brings HT 3.0 Performance and Architectural Latitude to HTX Connector

- Triples HT Clock Rate While Preserving Signal Integrity

- Leverages HT 3.0 Clock Recovery "Scrambling" and "Training" Features

- Adds Power Management Features

- Adds Link-Splitting Capability

- Allows Subsystem Connection to 2 CPUs

## *HTX3*<sup>™</sup> Features Summary

| Feature                          | HTX         | HTX3         | Notes                                                         |

|----------------------------------|-------------|--------------|---------------------------------------------------------------|

| Max Clock Rate                   | 800 MHz     | 2.6 GHz      | 12" Trace length                                              |

| Max Bandwidth x Lane             | 1.6 GT/s    | 5.2 GT/s     | Bi-directional                                                |

| Max Bandwidth Aggregate          | 6.4<br>GB/s | 20.8<br>GB/s | Bi-directional 16-Bit HT link                                 |

| HT3 Link Splitting Support       | NO          | YES          | HT link can be 1x 16-Bit or<br>2x 8-Bit for mutli-CPU support |

| HT3 Extended Power<br>Management | NO          | YES          | LDTREQ# Signal Added to<br>participate in x86 power states    |

| Extended FPGA Guidelines         | NO          | YES          | Incorporated field-proven recommendations                     |

| Full Backward Compatibility      |             | YES          | Level shifters and signal allocation                          |

## Why HyperTransport<sup>™</sup> *HTX3*<sup>™</sup>?

- FPGAs Play Key Role in Compute-Intensive Designs

- HTX3 Well Aligns with Expected FPGA Technology Progress

- FPGA Cores Expected to Support HT3.0-Class Clock Rates

- From Bandwidth Bottlenecks to Drivers

- Power Optimization Ranks High in HPC Agenda

- HT 3.0 Has Reached Maturity and Stability

- Design Learning Curve

- Product Implementations

- Market Feedback

- HT 3.0 Capability Now Safely and Stably "Connectorized"

# **Main Applications**

#### *HTX*<sup>™</sup> Applications

#### **Compute-Intensive Board Level Subsystems Requiring:**

- High Bandwidth + Low Latency

- Multi-CPU Connections (HTX3)

- Advanced Power Management (HTX3)

#### **Targeting:**

- Database Analytics

- Stock Trading Acceleration

- High-Traffic Web-Based Applications

- Transaction Servers

- Streaming Media Servers

- Storage Servers

- Server Clustering and SMP

- Financial Modeling

- Communications

- Content Processing

- Security Processing

- High-Perf Real World Rendering

# **Core Values**

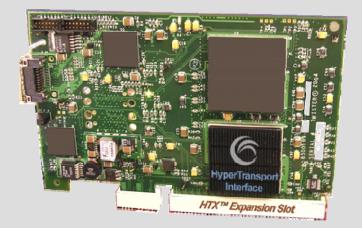

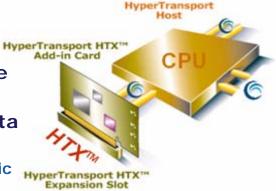

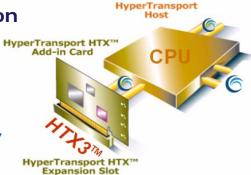

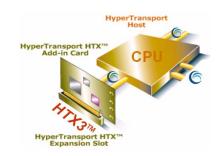

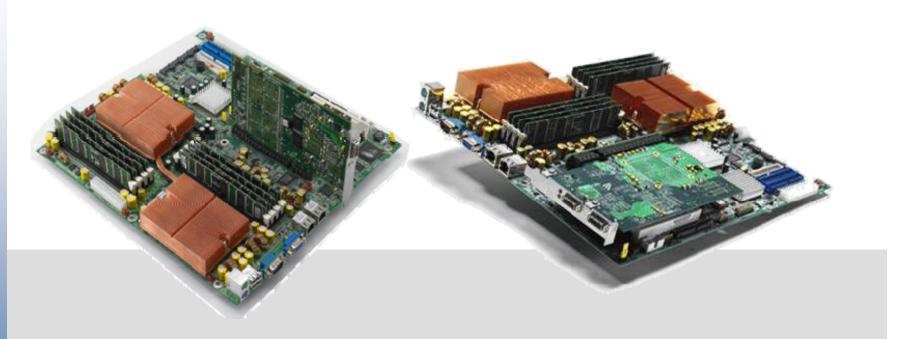

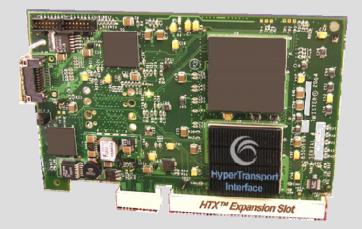

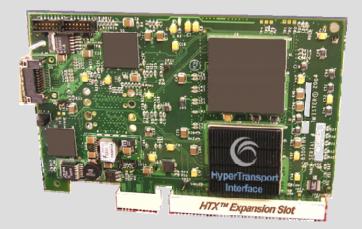

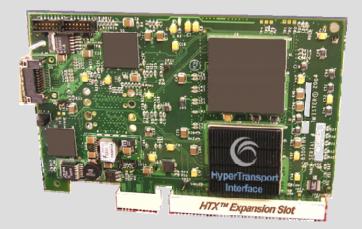

## *HTX*<sup>™</sup> and *HTX3*<sup>™</sup> Connector

- Uses popular PCI e Connector

- High-volume part, Low cost

- HT-defined signals

- Reverse-Installed vs. PCIe Slots

- Prevents Wrong Card Insertion

# *HTX*<sup>™</sup> and *HTX3*<sup>™</sup> Connector Mounting

Vertical Mount

Horizontal Mount via HTX Riser

### **Lowest Achievable Latency**

#### **No Control Logic Penalty**

#### **Control Logic Penalty**

#### Lowest Achievable Latency (cont.)

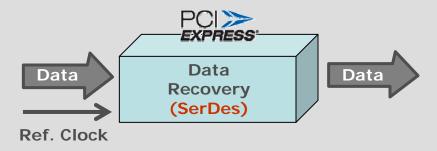

#### No 8B/10B Overhead Penalty

#### 20% 8B/10B Fixed Overhead Penalty

#### Lowest Achievable Latency (cont.)

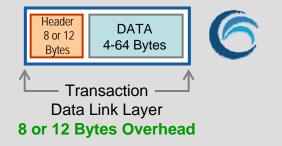

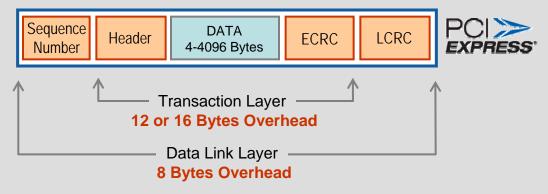

#### **Minimized Packet Overhead**

#### 12 Byte Overhead Penalty vs. HT

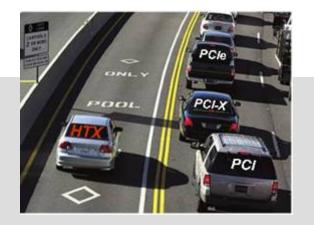

# **HTX**<sup>™</sup> Delivers the Extra Performance that PCI-Class Interfaces Cannot Deliver

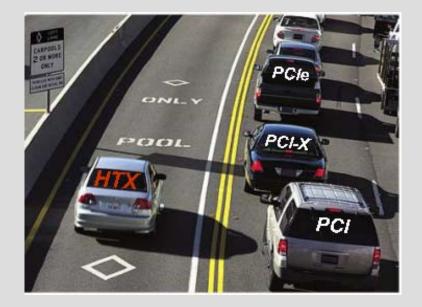

#### Complements PCIe and PCI-X

Cohexists within Same System

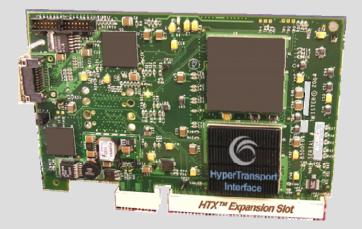

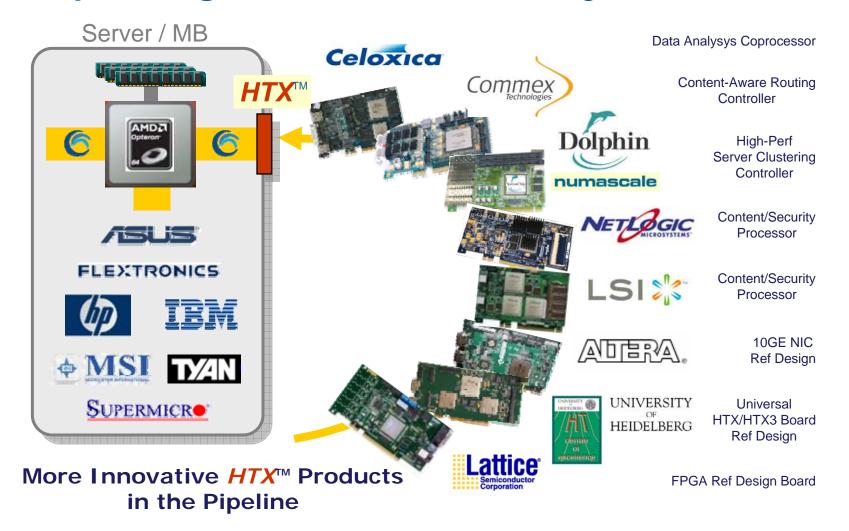

# **Product Ecosystem**

## Expanding *HTX*<sup>TM</sup> Products Ecosystem

# **Development Support**

## **HTX<sup>™</sup> Development Support**

#### HyperTransport Center of Excellence Design Support and Services

#### **Universal Board Reference Designs**

*HTX*™

*HTX3*<sup>™</sup>

HT and cHT Cores

Design Support Product Validation

**HTX<sup>™</sup> Development Support** (cont.)

# ATERA.

## HTX ™ 10GE NIC Design Kit

- Validated and Tested 10 Gigabit Ethernet Solution

- Dowloadable Free-of-Charge from HTC Web Site

•2x 10GE Ports •Stratix II FPGA

#### Fast Time-to-Market

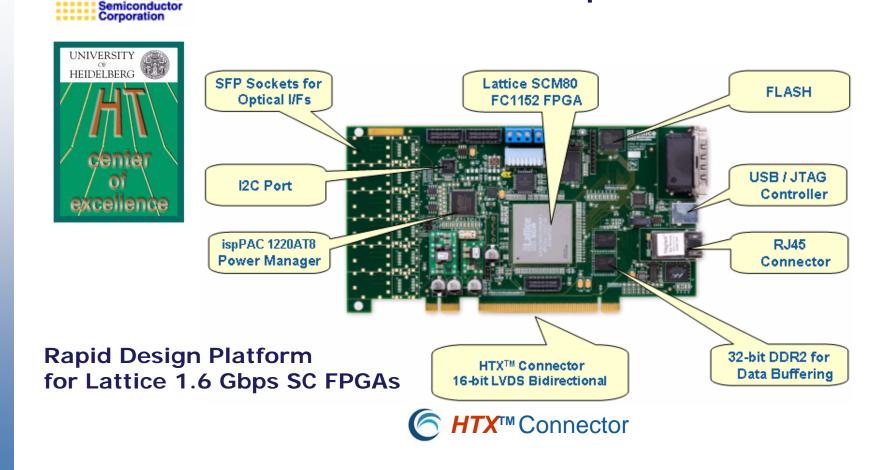

Lattice

## **HTX<sup>™</sup> Development Support** (cont.)

**HTX** TM FPGA Development Board

# **BIOS Support**

## **HTX<sup>™</sup> BIOS Support**

#### Consortium-Defined and Standardized *HTX*<sup>™</sup> BIOS Specifications

#### **Cross-Compatibility**

Fast Time-to-Market

# Why HTX?

## **Unique Technical Values**

#### HTX<sup>™</sup> Provides Superior Performance and Architectural Capabilities In Line with HPC Market Expectations

## **HTX**<sup>M</sup> Complements PCI Express

With its Unique Architectural and Performance Edge over General Purpose Interconnects, HTX is an Ideal Complement to PCI-Class Slot Connector Interfaces

## **HTX<sup>™</sup> Business Values**

# *HTX*<sup>™</sup> is a Competitive Differentiator for High-Performance Total Solution Vendors

- Negligible BOM Cost

- Leverages PCIe Economy of Scale

- System Flexibility

- Single MB Serves Multiple Markets

#### Growing HTX Subsystem Portfolio

- Coprocessors, Accelerated 10GE, ccNUMA Cluster Controllers, Content Processors, Others Released Soon

- Up-Selling Enabler

- Delivers Greater End-User Value

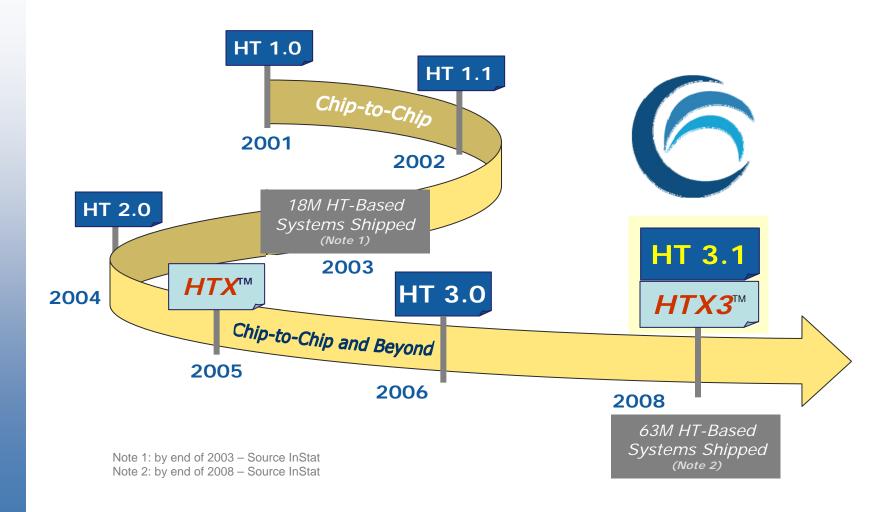

# With HyperTransport<sup>™</sup> The Technology Industry Wins

## Tangibility

Chosen by Industry Leaders Massive Market Penetration 60M+ HT Systems Shipped

# Investment Preservation

100% Specs Legacy Compatibility Smooth Product Migration Future-Ready