# **Standard Dimensions and Tolerances**

## **Conductors**

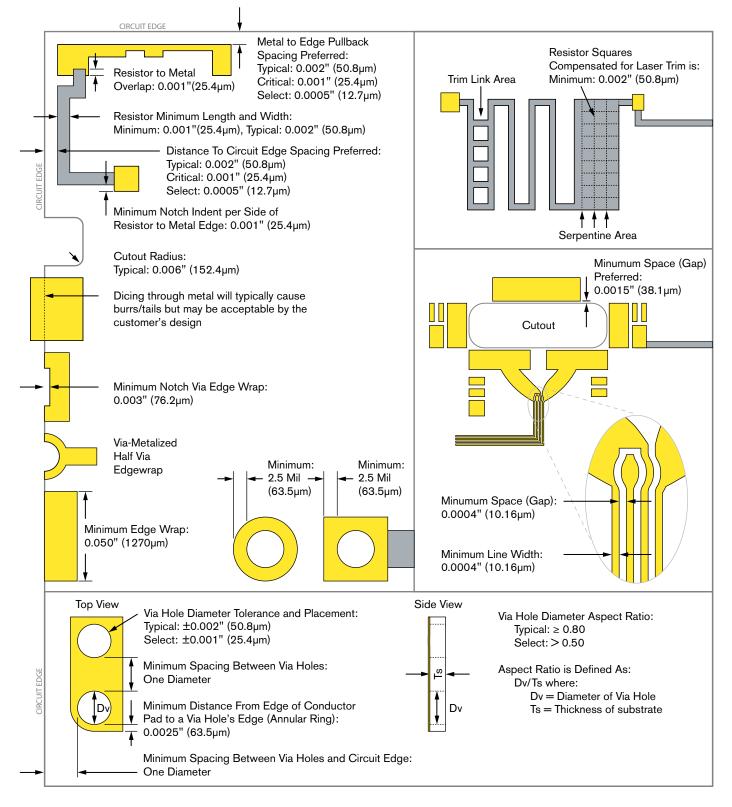

**Au: Minimum Line-Width (Trace)** Typical: 0.0004" (10.16μm) for <200μ" thick. Contact Sales for smaller dimensions.

**Au: Minimum Gap (Space)** Typical: 0.0004" (10.16μm) for <200μ" thick. Contact Sales for minimum gap for etchback.

$\begin{array}{l} \mbox{Cu: Minimum Line-Width (Trace)} \\ \mbox{Typical: 0.0004" (10.16 \mu m) for} \\ < 200 \mu " thick. \\ \mbox{Contact Sales for Cu } > 200 \mu " thick. \end{array}$

$\begin{array}{l} \mbox{Cu: Minimum Gap (Space)} \\ \mbox{Typical: 0.0004" (10.16 \mu m) for} \\ \mbox{<200 } \mu " \mbox{thick.} \\ \mbox{Contact Sales for Cu $>$200 $ \mu " \mbox{thick.}} \end{array}$

**Cu or Au: Maximum Thickness** Maximum: 0.002" (50.8µm) Contact Sales for details.

## Tolerances

# Au: Dimensional Tolerance on Critical Areas

Typical: ±0.0002" (5.08μm) Critical: ±0.0001" (2.54μm) Select: ±0.00005" (1.27μm) Dimensional tolerance on non-critical areas: Typical: ±0.0002" (5.08μm)

### Cu or Au: Dimensional Tolerance on Critical Areas Where Cu is Thicker Than 0.0005" ( $500\mu$ ") or ( $12.7\mu$ m) Typical: $\pm 0.0003$ " ( $7.62\mu$ m) Select: $\pm 0.0002$ " ( $5.08\mu$ m) Dimensional tolerance on non-critical

areas: Typical: ±0.0004" (10.16µm)

#### Resistors

#### **Resistor Minimum Length and Width**

Minimum: 0.001" (25.4µm) Typical: 0.002" (50.8µm) Contact Sales for dimensions which will require a relaxed tolerance.

Resistor Tolerance (With Laser Trim) Typical:  $\pm 2.0\%$ Select:  $\pm 0.5\%$ Select is dependent on size of resistor.

#### Vias - Hollow

Via Hole Diameter Aspect Ratio: Typical:  $\ge 0.80$ Select:  $\ge 0.50$ Aspect ratio is defined as:  $D_v / T_s$  where:  $D_v =$  Diameter of the via (thru hole)  $T_s =$  Thickness of the substrate

**Via Hole Diameter Tolerance** Typical: ±0.002" (50.8µm) Select: ±0.001" (25.4µm)

Via Hole Location Tolerance

Typical: ±0.002" (50.8μm) Select: ±0.001" (25.4μm)

Via Hole Taper Typical: 10% Select: ±0.001" (25.4µm)

Via Hole Spacing (Hollow Plated) One diameter minimum distance

Via Hole Proximity to Edge of Circuit One diameter minimum distance away from edge

# Via to Pattern Registration (Hollow Plated)

Typical:  $\pm 0.002''$  (50.8µm) Select:  $\pm 0.0005''$  (12.7µm) Contact Sales for details.

Front to Back Image Registration Typical:  $\pm 0.001"$  (25.4µm) Select:  $\pm 0.0005"$  (12.7µm)

### For Solid Filled Vias see page 27

#### Laser

**Laser Machined Features** Typical: ±0.002" (50.8µm) Select: ±0.001" (25.4µm)

# Laser Machined Features Next to Au/Sn

Minimum distance:  $0.005'' (127 \mu m)$ for Al<sub>2</sub>O<sub>3</sub> Minimum distance:  $0.010'' (254 \mu m)$ for AlN Minimum distance:  $0.010'' (254 \mu m)$ for BeO

### Laser Machined Radius

Typical: 0.006" (152.4μm) Select: 0.003" (76.2μm)

### Dicing

**Circuit Dimensional Tolerance**– **Diamond Sawn** Typical: ±0.002" (50.8μm) Critical: ±0.001" (25.4μm) Select: ±0.0005" (12.7μm)

#### Via Trench Cut Depth Tolerance

Typical: ±0.002" (50.8µm)

Dicing through metals will typically cause burrs/tails and on polished materials could affect adhesion. Another solution ATP recommends to prevent these type of issues is by putting a pullback typical .001" (0.0254mm) in the design of the circuit. Inquire with ATP Sales for more information.

Diamond sawing (dicing), scribing, or breaking of cut thru edge vias or castellations may cause undercutting or separation induced anomalies. If it is required by design, then ATP will refer and adhere to MIL-STD-883J Section 3.1.1.3.

### **Notes and Recommendations**

Note: For long term storage, ATP recommends storing thin-film circuits ideally at room temperature in a nitrogen purged dessicator (or equivalent) and using a preclean method that is compatible with thinfilm circuits prior to assembly.

Note: ATP is a fabricator of custom thinfilm circuits and does not claim to be an electrical design consultant. ATP does not guarantee electrical performance of any customer supplied custom designs.

Note: All thin-film circuits shipped from ATP are free of debris and FOD when packaged. However, alumina and other hard substrate materials have very sharp corners and edges that can act like knife edges and may create debris and FOD from the packaging materials used during the shipping process. Some large and unusually shaped circuits may require a special foam insert to ensure breakage does not happen during shipping. ATP makes every effort to ship clean and QC approved thin-film circuits but it is for these reasons ATP recommends using a pre-clean method that is compatible with thin-film circuits prior to assembly.

For more information on dimension and tolerances, request document #DG50020 "Design For Manufacturability."

# Standard Dimensions and Tolerances (Continued)

#### **Design Guideline Dimensions and Tolerances**

ATP is a fabricator of custom thin film circuits and does not claim to be an electrical design consultant. ATP does not guarantee electrical performance of any customer supplied custom designs. All prints supplied need to be at final dimension and not biased.