Security Transponder, Micro-RISC Kernel and Radio Transmitter (SMART)

**Product Specification**

2011 Nov 17

Confidential

# PCF7961XTT

# CONTENTS

| 1 FEATURES                                           | 6  |

|------------------------------------------------------|----|

| Calculation Unit                                     | 6  |

| Security Transponder Emulation                       | 6  |

| RISC Controller                                      | 6  |

| UHF Transmitter                                      |    |

| 2 GENERAL DESCRIPTION                                |    |

| 3 ORDERING INFORMATION                               |    |

| 4 TYPICAL APPLICATION                                |    |

| 5 BLOCK DIAGRAM                                      | 8  |

| Contactless Interface                                |    |

| Power Management                                     | 8  |

| Calculation Unit                                     |    |

| Test/Debug Logic                                     |    |

| RISC Controller                                      |    |

| UHF Transmitter                                      |    |

| 6 QUICK REFERENCE DATA                               |    |

| Transponder Emulation                                |    |

| RISC Operation<br>UHF Transmitter                    |    |

| 7 PINNING                                            | -  |

| 7 PINNING<br>8 POWER MANAGEMENT DESCRIPTION          |    |

| 8.1 Supply Switch Logic                              |    |

| 8.1 Supply Switch Logic<br>Presence of LF Field      |    |

| Port Wake Up (button press)                          |    |

| Presence of LF Field and Port Wake Up (button press) |    |

| 8.2 Device Operating Modes                           |    |

| 8.2.1 POWER-OFF Mode                                 |    |

| 8.2.2 BATTERY Mode                                   |    |

| 8.2.3 TRANSPONDER Mode                               |    |

| 8.3 Port Sense Logic                                 |    |

| 8.4 Power Management Control Register                |    |

| FLD, Field Detected                                  |    |

| PMODE, Power Mode                                    |    |

| PBAT, Power from Battery                             | 17 |

| PLF, Power from LF Field                             |    |

| RST, RESET device                                    | 17 |

| NMI, Non Maskable Interrupt control                  | 17 |

| IDLE, IDLE Mode                                      | 18 |

| 9 CONTACTLESS INTERFACE DESCRIPTION                  | 18 |

| 9.1 LF Rectifier and Voltage Limiter                 | 18 |

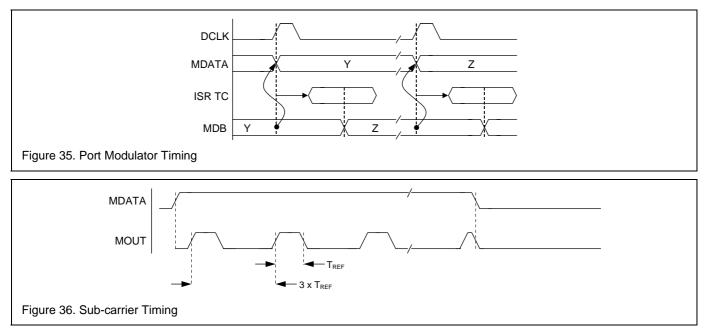

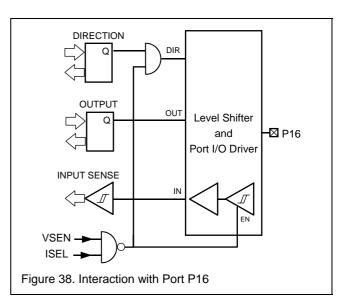

| 9.2 Modulator                                        | 18 |

| 9.3 Demodulator                                      |    |

| LFEN, LF Demodulator Enable                          |    |

| LFD, LF Demodulator Data                             |    |

| 9.4 LF Field Detection                               |    |

| FLD, Field Detected                                  |    |

| 10 RISC CONTROLLER DESCRIPTION                       |    |

| 10.1 Application Code Memory                         |    |

| 10.2 System Code Memory                              |    |

| Boot Routine                                         |    |

| ROM Library                                          |    |

| In-Circuit Monitor and Download Routine              | 23 |

| 10.3 Data Memory                                      | 23 |

|-------------------------------------------------------|----|

| 11 PERIPHERIAL DESCRIPTION                            | 24 |

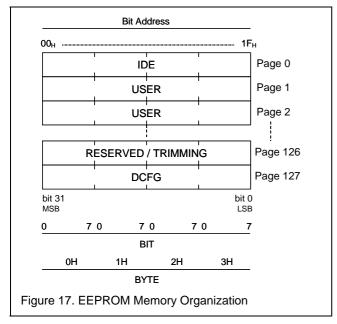

| 11.1 EEPROM                                           | 25 |

| 11.1.1 Organisation                                   | 25 |

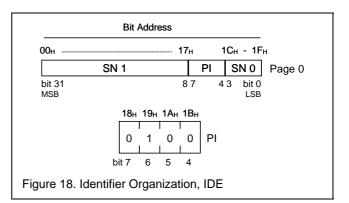

| 11.1.1.1 Identifier, IDE                              | 25 |

| 11.1.1.2 Device Configuration Page, DCFG              | 25 |

| TEN, Transponder Emulation Enable                     | 26 |

| 11.1.2 High-Level EEPROM Access                       | 26 |

| 11.1.3 Low-Level EEPROM Access                        | 26 |

| Read Operation                                        | 27 |

| Write Operation                                       | 27 |

| POEE, Power On EEPROM                                 | 28 |

| PG[60], Page Address                                  | 28 |

| BYTE[10], Byte Address                                | 28 |

| BIT[20], Bit Address                                  | 28 |

| WR, Select Write/Read                                 | 28 |

| EEIO, EEPROM Data I/O                                 | 28 |

| BUSY, Busy                                            | 29 |

| PERR, Programming Error                               | 29 |

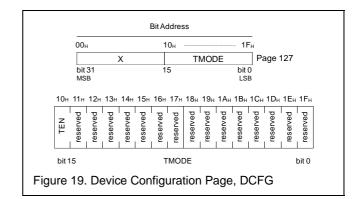

| 11.2 Interrupt System and IDLE Control.               | 30 |

| 11.2.1 Interrupt Enable Register                      | 31 |

| 11.2.2 Interrupt Request Flags                        |    |

| 11.2.3 Interrupt Source Assignment                    |    |

| 11.2.4 Interrupt Service                              | 31 |

| 11.2.5 IDLE mode                                      | 31 |

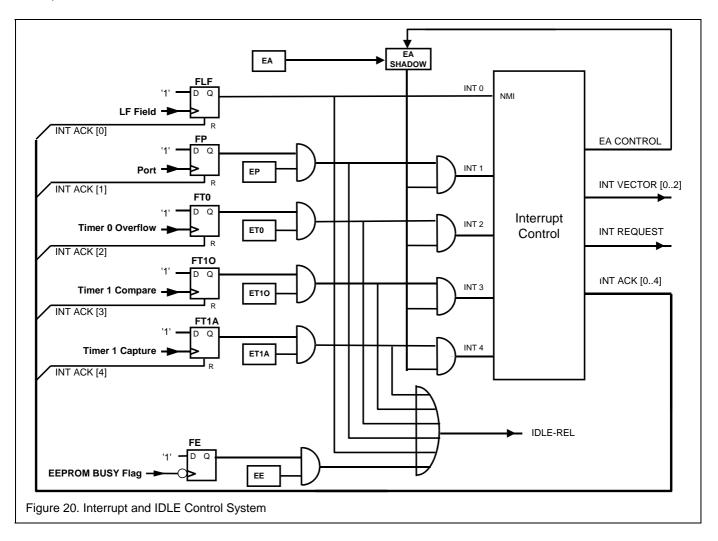

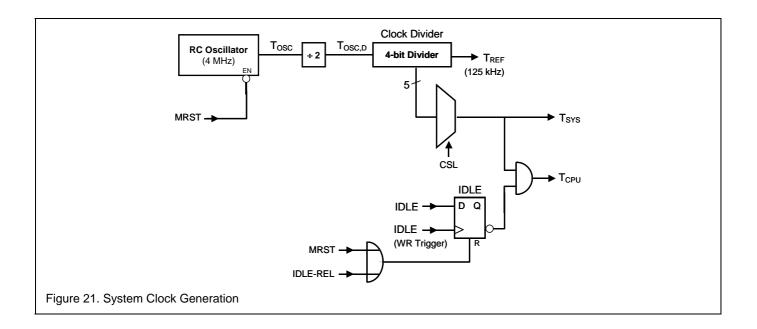

| 11.3 System Clock Generation                          | 33 |

| CSL[20], Clock Select                                 | 33 |

| IDLE Mode                                             |    |

| T <sub>REF</sub> , Reference Clock                    | 34 |

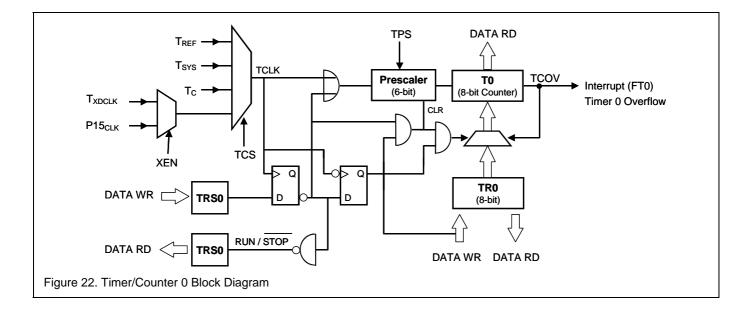

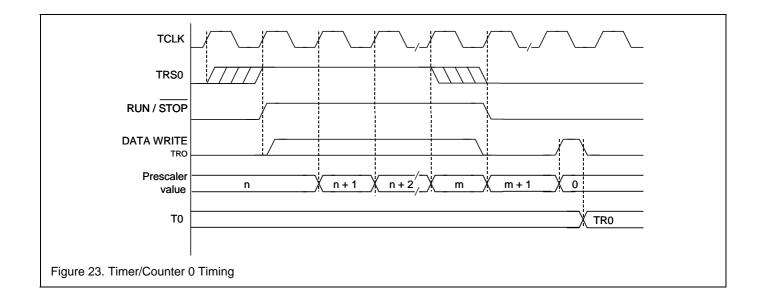

| 11.4 Timer/Counter 0                                  | 35 |

| TCS[10], Timer/Counter 0 Clock Source                 | 35 |

| TPS[20], Timer/Counter 0 Prescaler                    |    |

| TRS0, Timer/Counter 0 Run/Stop                        |    |

| TR0, Timer/Counter 0 Reload                           |    |

| T0, Timer/Counter 0 Counter Register                  |    |

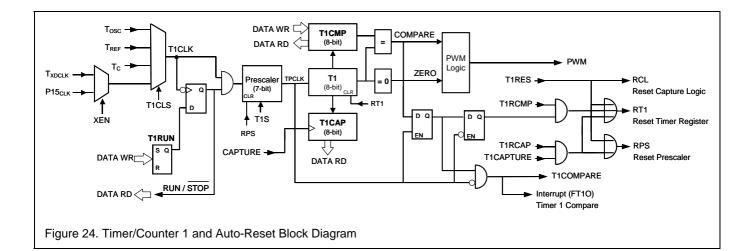

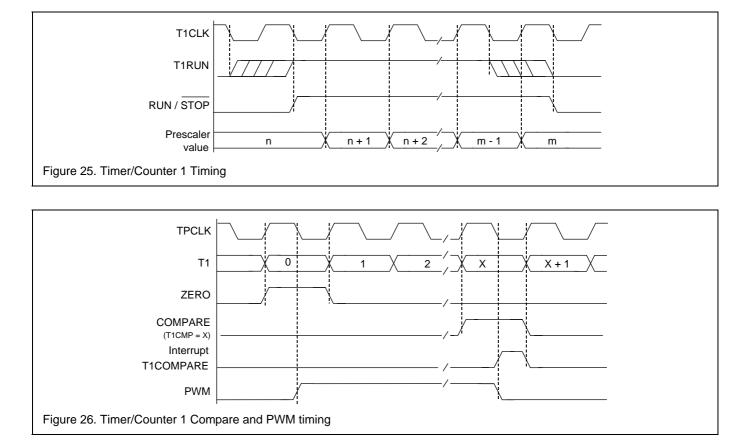

| 11.5 Timer/Counter 1                                  |    |

| T1CLS[1,0], Timer/Counter 1 Clock Source              |    |

| T1S[20], Timer/Counter 1 Prescaler Select             |    |

| T1RUN, Timer/Counter 1 Run/Stop                       |    |

| T1CMP, Timer/Counter 1 Compare Register               |    |

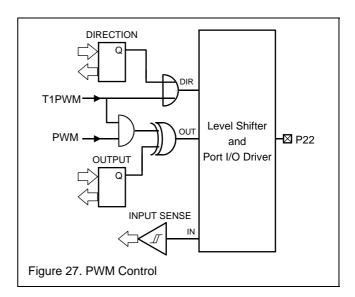

| T1PWM, Timer/Counter 1 Pulse Width Modulation Control | 39 |

| T1CAP, Timer/Counter 1 Capture Register               | 40 |

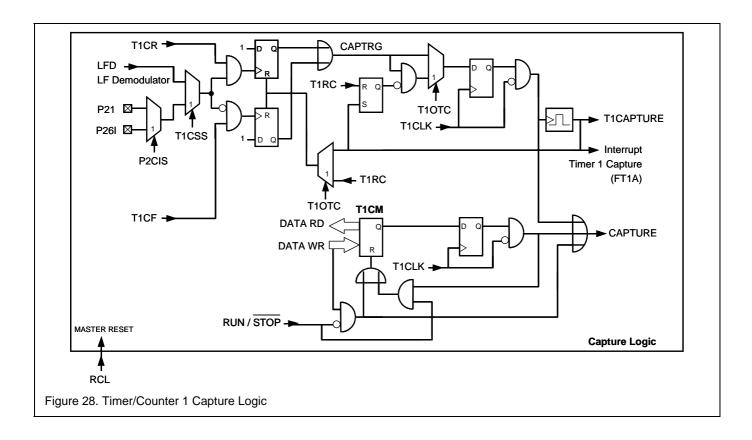

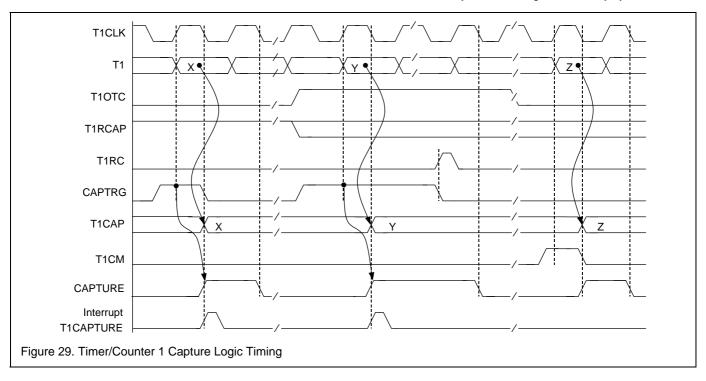

| T1CSS, Timer/Counter 1 Capture Source Select          | 40 |

| T1CR and T1CF, Timer/Counter 1 Capture Configuration  | 41 |

| T1CM, Timer/Counter 1 Capture Manual                  | 41 |

| T1OTC, Timer/Counter 1 One Time Capture               | 41 |

| T1RC, Timer/Counter 1 Reset Capture                   | 41 |

| T1RES, Timer/Counter 1 Reset                          | 42 |

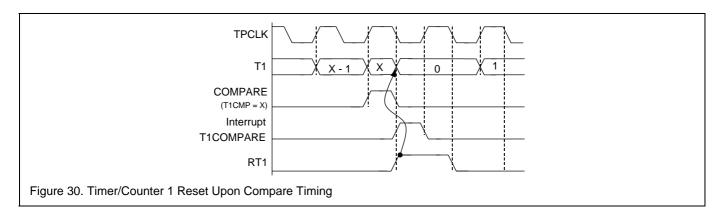

| T1RCMP, Timer/Counter 1 Reset Upon Compare            | 42 |

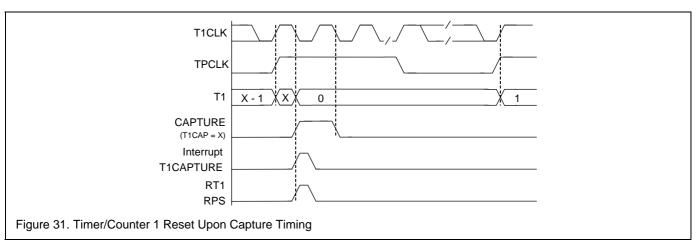

| T1RCAP, Timer/Counter 1 Reset Upon Capture            | 42 |

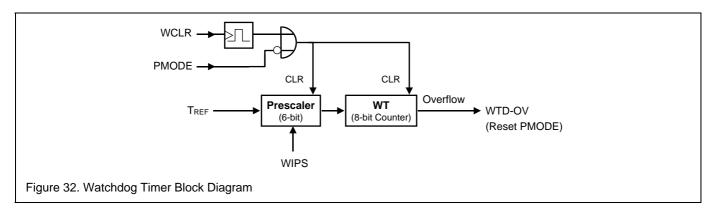

| 11.6 Watchdog Timer, WT                               | 43 |

| WPS[20], Watchdog Prescaler Select                    | 43 |

| WCLR, Watchdog Clear                                  | 43 |

|                                                       |    |

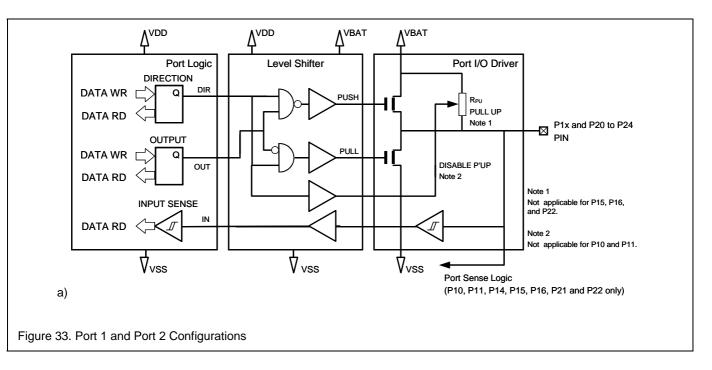

| 11.7 I/O Ports                                                      |    |

|---------------------------------------------------------------------|----|

| P10, P11, P14 to P16, P21 and P22, Wake-Up Sense and Port Interrupt | 45 |

| P15, External Clock Input                                           |    |

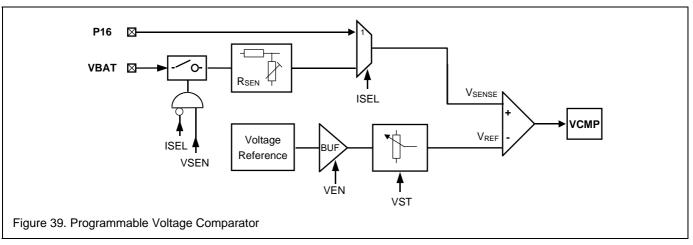

| P16, Voltage Comparator Input                                       | 45 |

| P17, P20, Digital Modulator Output                                  | 45 |

| P21, Timer 1 Capture Trigger Input                                  | 45 |

| P22, Timer 1 PWM Output                                             | 45 |

| 11.7.1 PxDIR, Port Direction Control                                |    |

| IO2x, Port Direction Control                                        | 46 |

| P21WD, Port 21 Wake Up Disable                                      |    |

| P2CIS, Port 2 Capture Input Source                                  |    |

| 11.7.2 PxOUT, Port Output Control                                   | 46 |

| 11.7.3 PxINS, Port Input Sense                                      | 46 |

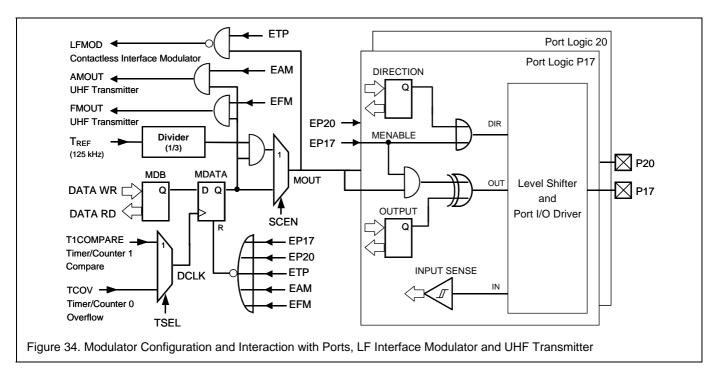

| 11.8 Digital Modulator                                              | 47 |

| EP17, Enable P17                                                    | 47 |

| EP20, Enable P20                                                    | 47 |

| ETP, Enable Transponder                                             | 47 |

| EAM, Enable Amplitude Modulation                                    | 47 |

| EFM, Enable Frequency Modulation                                    | 47 |

| TSEL, Timer Select                                                  |    |

| MDB, Modulator Data Bit                                             |    |

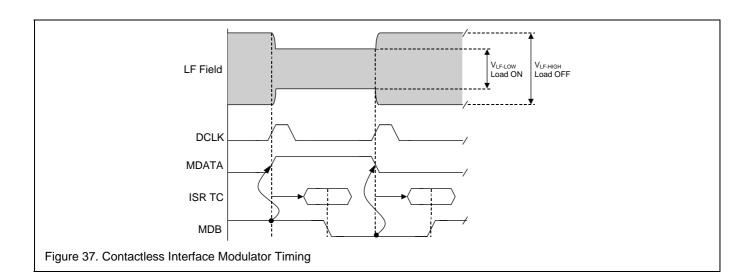

| SCEN, Sub-Carrier Enable                                            |    |

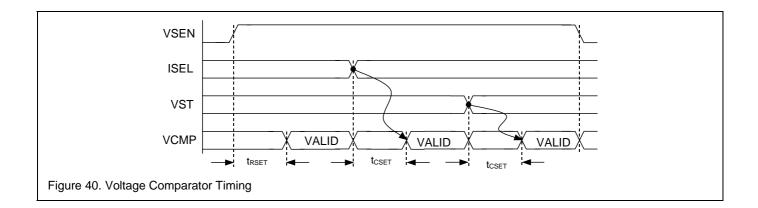

| 11.9 Voltage Comparator                                             | 50 |

| VSEN, Voltage Comparator Enable                                     |    |

| ISEL, Input Select                                                  |    |

| VCMP, Voltage Compare                                               | 51 |

| VST, Reference Voltage Set                                          | 51 |

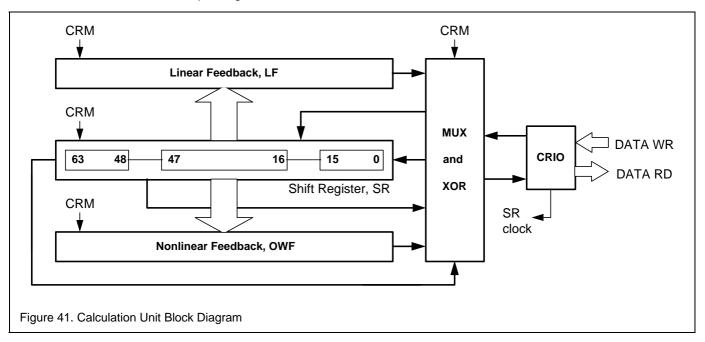

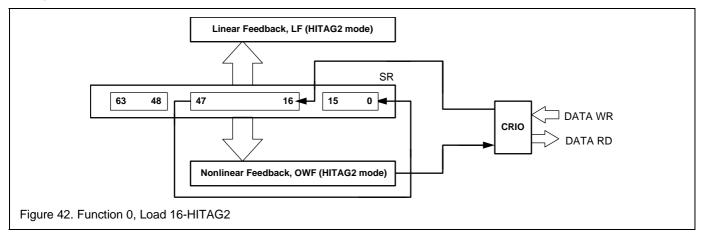

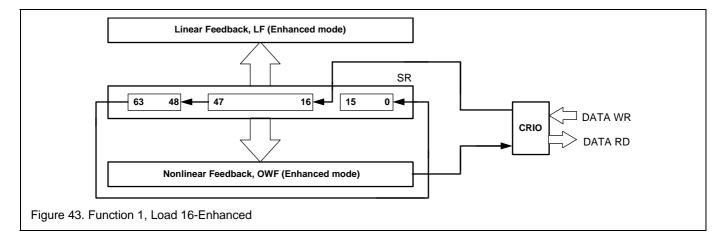

| 11.10 Calculation Unit                                              | 52 |

| Function 0, Load 16-HITAG2                                          | 54 |

| Function 1, Load 16-Enhanced                                        | 54 |

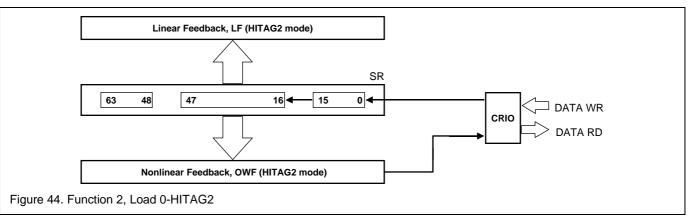

| Function 2, Load 0-HITAG2                                           | 55 |

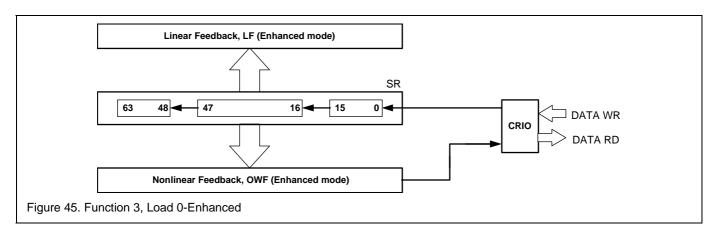

| Function 3, Load 0-Enhanced                                         | 55 |

| Function 4, LF-HITAG2                                               | 56 |

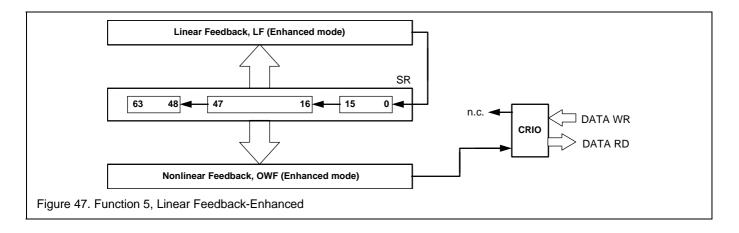

| Function 5, LF-Enhanced                                             | 56 |

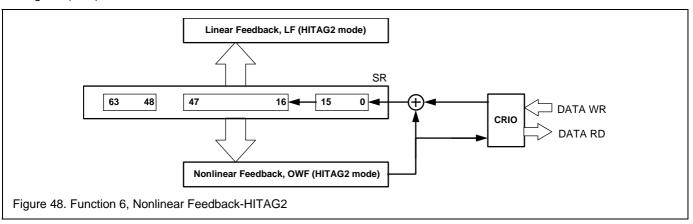

| Function 6, OWF-HITAG2                                              | 57 |

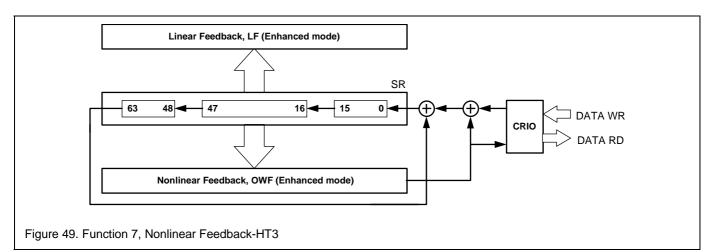

| Function 7, OWF-Enhanced                                            | 57 |

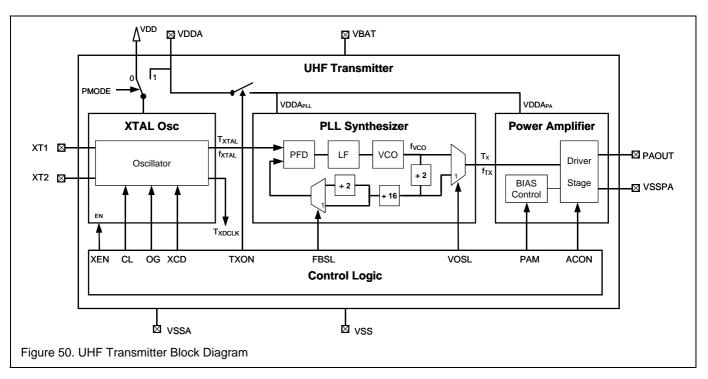

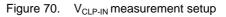

| 2 UHF TRANSMITTER DECRIPTION                                        | 58 |

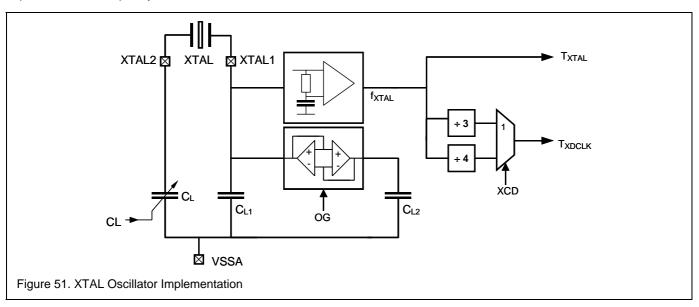

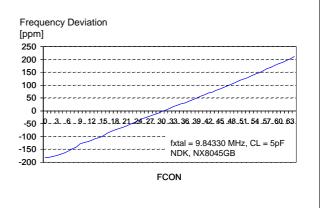

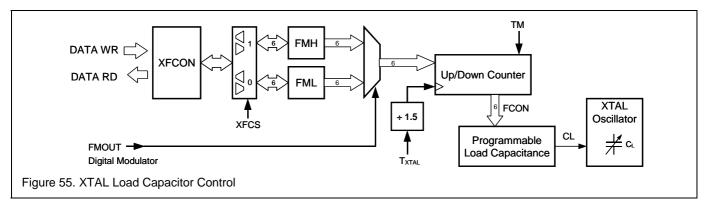

| 12.1 XTAL Oscillator                                                | 59 |

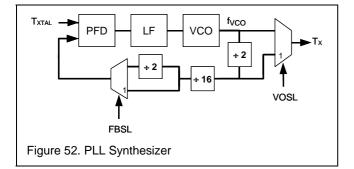

| 12.2 PLL Synthesizer                                                | 60 |

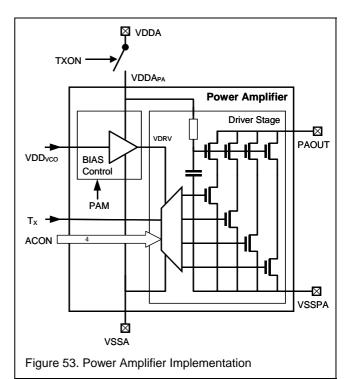

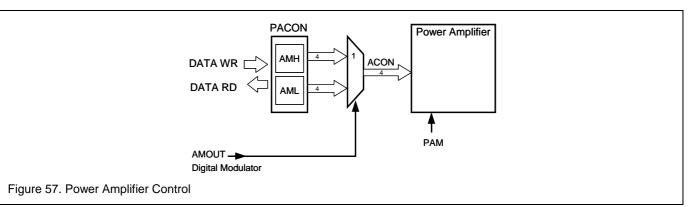

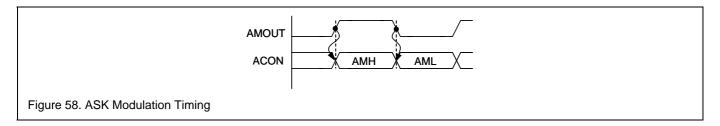

| 12.3 Power Amplifier                                                | 60 |

| 12.4 Control Logic                                                  |    |

| 12.4.1 Transmitter Set-Up and General Control                       |    |

| FBSL, PLL Feedback Select                                           |    |

| VOSL, VCO Output Select                                             |    |

| OG, XTAL Oscillator Gain Control                                    |    |

| XCD, XTAL Clock Divider                                             |    |

| XEN, XTAL Oscillator Enable                                         |    |

| TXON, Transmitter Power On                                          |    |

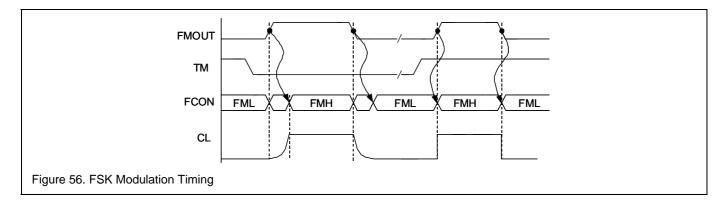

| 12.4.2 XTAL Oscillator Control and FSK Modulation                   |    |

| XFC[50], XTAL Oscillator Frequency Control                          |    |

| XFCS, XTAL Frequency Control Select                                 |    |

| TM, Transparent Mode                                                |    |

| 12.4.3 Power Amplifier Control and ASK Modulation                   |    |

|                                                                     |    |

| AMH[30], Amplitude Modulation HIGH                                    |    |

|-----------------------------------------------------------------------|----|

| AML[30], Amplitude Modulation LOW                                     |    |

| PAM[1,0], Power Amplifier Mode                                        | 66 |

| 13 DEVICE MODES                                                       | 67 |

| INIT Mode                                                             | 67 |

| PROTECTED Mode                                                        | 67 |

| TAMPERED Mode                                                         | 67 |

| VIRGIN Mode                                                           | 67 |

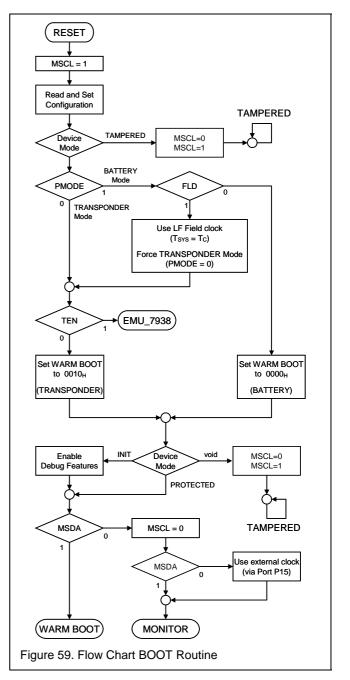

| 14 BOOT ROUTINE                                                       |    |

| 14.1 Functional Description                                           | 68 |

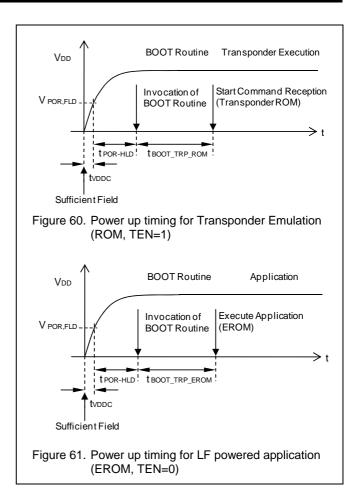

| 14.2 Execution Time                                                   |    |

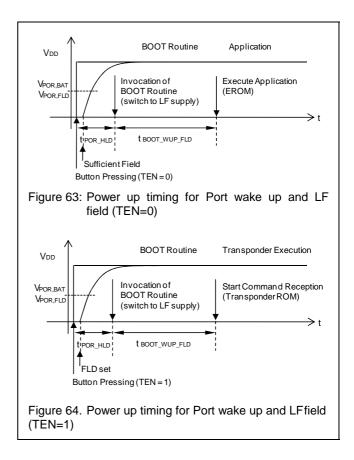

| Presence of LF Field                                                  |    |

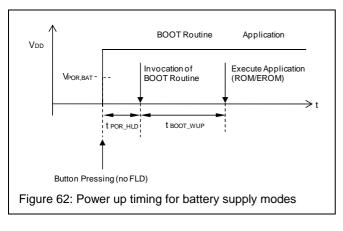

| Port Wake Up (button press)                                           |    |

| Presence of LF Field and Port Wake Up (button press)                  |    |

| 15 MONITOR AND DOWNLOAD INTERFACE                                     |    |

| 16 EEPROM CONTENT AT DELIVERY                                         |    |

| 17 LIMITING VALUES                                                    |    |

| 18 ELECTRICAL CHARACTERISTICS                                         |    |

| 18.1 Operating Conditions                                             |    |

| 18.2 AC/DC Characteristics                                            |    |

| 18.3 UHF Transmitter Operating Conditions                             |    |

| 18.4 UHF Transmitter AC/DC Conditions                                 |    |

| 19 TIMING CHARACTERISTICS                                             |    |

| 19.1 General                                                          |    |

| 19.2 Contactless Interfaces                                           |    |

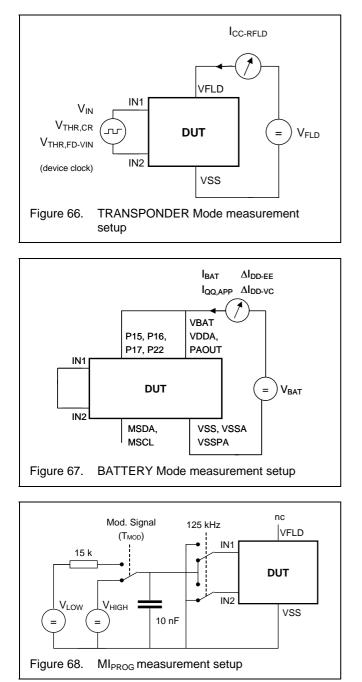

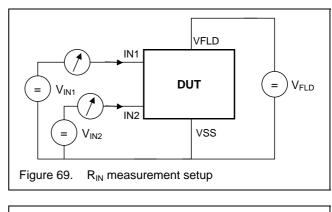

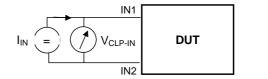

| 20 TEST SETUP                                                         |    |

| 21 ANOMALY NOTES                                                      |    |

| 21.1 Reading of UHF Transmitter is not supported with LF Field supply |    |

| 22 APPLICATION NOTES                                                  |    |

| 22.1 Selecting the capacitor C <sub>VFLD</sub> properly               |    |

| 22.2 Avoid leakage current in POWER-OFF mode                          |    |

| 22.3 LED output configuration                                         |    |

| 22.4 Avoid device Lock-Up in INIT                                     |    |

| 22.5 Entering POWER-OFF Mode                                          |    |

| 22.6 Entering TRANSPONDER Mode                                        |    |

| 22.7 Avoid accidental device Wake Up                                  |    |

| 22.8 Usage of control bit NMI                                         |    |

| 22.9 Device operating mode after battery power-up.                    |    |

| 22.10 Controlling the XTAL Oscillator Gain properly                   |    |

| 22.11 System Test by monitoring internal clock signals                |    |

| 23 RELATED DOCUMENTS                                                  |    |

| 24 DEVELOPMENT TOOLS                                                  |    |

| 25 REVISION HISTORY                                                   |    |

| 26 LEGAL INFORMATION                                                  |    |

| 26.1 Data sheet status                                                |    |

| 26.2 Definitions                                                      |    |

| 26.3 Disclaimers                                                      |    |

| 27 Contact information                                                | 91 |

# PCF7961XTT

# **1 FEATURES**

- Single chip Security Transponder and Keyless Entry solution with on-chip UHF Transmitter

- Up to seven keyless Entry command buttons

- RISC programmable device features

- 512 Byte EEPROM for extended data storage

- 32 bit quasi unique device and product type identification

- Device supply may be derived from LF Field

- Single Lithium cell operation, 2.1V to 3.6V

- 20-Pin TSSO package

### **Calculation Unit**

- Hardwired security algorithm

- HT2 48 bit Secret Key

- HT3 96 bit Secret Key

# **Security Transponder Emulation**

- HT3 compatible Transponder operation

- 96 bit secret key authentication

- Up to 460 Byte User EEPROM size

- Fast mutual authentication, 53ms (96 bit Secret Key)

- HT2 compatible basic command set and coding

- Versatile EEPROM access and protection capabilities

- Improved Transponder Command error handling

- Excellent sensitivity in read and write mode

### **RISC Controller**

- 8 Bit RISC Architecture (MRK II)

- 16 kByte E-ROM or 4/8 kByte ROM (application)

- 4 kByte ROM (device firmware and library functions)

- 192 Byte User RAM

- 7 general purpose I/O

- Two 8 Bit Timer/Counter

- Watchdog

- Single level interrupt architecture

- On-chip RC Oscillator (< ±8%)

- Short instruction execution time (as fast as 0.5µs)

- Low power consumption RUN: 300μA, IDLE: 20μA, PD: 100nA

- Programmable battery low detection

### **UHF Transmitter**

- Highly integrated PLL stabilized design

- Carrier frequency 315MHz or 434MHz

- Programmable reference crystal load capacitance

- Programmable ASK and FSK modulation properties

- Up to 20 kbps modulation data rate (Manchester)

- Programmable and stabilized output power

- Low power consumption TRANSMIT: 9.8mA; 9dBm @ 434MHz LOCKED: 1.5mA

# **2 GENERAL DESCRIPTION**

The PCF7961X is a single chip solution for applications combining vehicle Immobilization and Keyless Entry functions (Combi Key) that require the transponder to offer extended data storage capabilities.

To serve the function of a Security Transponder, an external coil has to be connected to the device. Providing contactless communication with the base station as well as to derive the device power supply from the magnetic field, generated by a corresponding base station. No additional battery supply is needed. The basic transponder operation is emulated by the RISC and is functional compatible with the transponder PCF7938XA and features versatile EEPROM access and protection capabilities. The Security Transponder features secure contactless authentication, employing a Secret Key and a random number in order to cipher any communication between the device and the base station. The PCF7961X features a factory programmed quasi unique serial number that also serves as product type identification.

When serving Keyless Entry functions, the device is powered from an external battery. The application program and the hardwired Calculation Unit may accomplish rolling code generation. The Calculation Unit may operate in standard HT2 (48 bit Secret Key) or HT3 mode (96 bit Secret Key). A number of general purpose I/Os are provided for command buttons, LED, IR or other optional external circuitry. The on-chip UHF Transmitter requires no external components to operate at 315MHz or 434MHz except for the reference crystal and the loop antenna matching circuitry.

Device operation is controlled by an E-ROM (FLASH like features) based RISC Controller, powered by NXP's low power 8-Bit MICRO RISC KERNEL (MRK II). The RISC employs a 2-stage pipeline architecture in order to execute an instruction in a single clock cycle. Device timing is derived from an on-chip low tolerance RC Oscillator that provides a programmable system clock, with a frequency up to 2 MHz. The system clock may also be derived from the transponder interface, e.g. LF Field clock or the PLL reference clock, if desired.

The PCF7961X incorporates an advanced power management that supports voltage measurement for battery low detection. For increased battery lifetime, the device features an extremely low quiescent current in POWER-OFF state, achieved by disconnecting the battery from most of the internal circuitry. The device comes in a 20 pin TSSO Package.

The device is available as E-ROM product (FLASH like features) supporting in-circuit program download and debugging. The device is fully RoHS compliant and Dark Green (DG). DG means use of flame retardants free of halogen and antimony.

# PCF7961XTT

### **3 ORDERING INFORMATION**

| EXTENDED            | DESCRIPTION | PACKAGE<br>NAME OUTLINE VERSION |          | TEMPERATURE    |

|---------------------|-------------|---------------------------------|----------|----------------|

| TYPE NUMBER         | MEMORY TYPE |                                 |          | RANGE (°C)     |

| PCF7961XTT/C1AErrff | 16 KB EROM  | TSSOP20                         | SOT360-1 | -40°C to +85°C |

| PCF7961XTT/C1AE0915 | 16 KB EROM  | TSSOP20                         | SOT360-1 | -40°C to +85°C |

| PCF7961XTT/C1AC0915 | 8 KB EROM   | TSSOP20                         | SOT360-1 | -40°C to +85°C |

| PCF7961XTT/C1ACrrff | 8 KB EROM   | TSSOP20                         | SOT360-1 | -40°C to +85°C |

Note

- PCF7961XTT/C1AE0915 and PCF7961XTT/C1AC0915 represent the E-ROM product for development and applications with low quantities. E-ROM programming shall be performed by the customer. The Monitor and Download Interface (MSDA/MSCL) supports E-ROM download and ERASE/WRITE as fast as 700ms for 4 kByte.

- PCF7961XTT/C1AErrff and PCF7961XTT/C1ACrrff represent a customized product. The ROM Library is specified by a 2 digit code at location marked "rr". Under certain conditions, NXP may perform E-ROM programming with customer application code and customer EEPROM pattern. The customer E-ROM and EEPROM FabKey is specified by a 2 digit code at location marked "ff".

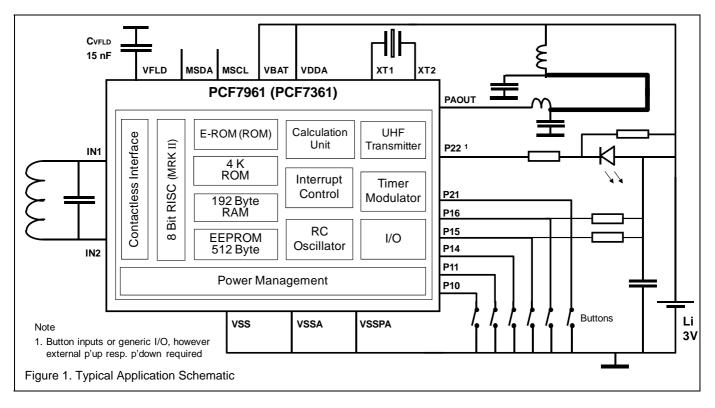

# **4 TYPICAL APPLICATION**

### Note

- 1. Since most of the device ports do not feature an on-chip pull-up or pull-down, corresponding application measures are required to avoid a floating port, when operating as input (e.g. during POWER-OFF mode). This is applicable for ports P15, P16 and P22.

- 2. The value of C<sub>VFLD</sub> need to be selected, according to the system properties, see section 22.1.

# PCF7961XTT

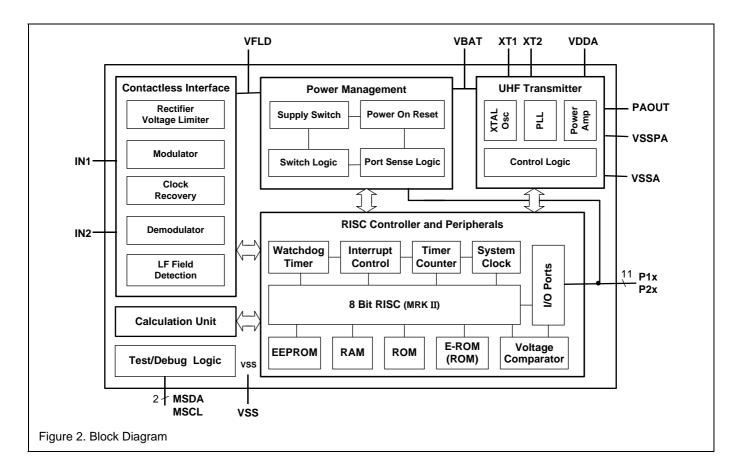

# **5 BLOCK DIAGRAM**

The PCF7961X features a high level of integration and requires few external components only, to operate as Security Transponder and/or Keyless Entry Solution. The device incorporates the following circuitry, see Figure 2.

# **Contactless Interface**

Rectifier and Voltage Limiter Modulator Clock Recovery Demodulator LF Field Detection

# **Power Management**

Supply Switch Supply Switch Logic Power On Reset Port Up Sense

### **Calculation Unit**

# **Test/Debug Logic**

# **RISC Controller**

8 Bit RISC (MRK II family) ROM, System Code Memory E-ROM (ROM), Application Code Memory RAM EEPROM Interrupt Control Timers / Counters I/O Ports Programmable Voltage Comparator System Clock (including on-chip RC oscillator) Watchdog Timer

# **UHF Transmitter**

XTAL Oscillator Phase Locked Loop (PLL) Power Amplifier Control Logic

# **6 QUICK REFERENCE DATA**

# **Transponder Emulation**

|                      | PARAMETER                         | VALUE                                                | UNIT               |  |  |  |

|----------------------|-----------------------------------|------------------------------------------------------|--------------------|--|--|--|

| Carrier frequency    | у                                 | 125                                                  | kHz                |  |  |  |

| Data rate READ       |                                   | 4.0                                                  | kbit/s             |  |  |  |

|                      | WRITE (typ)                       | 5.2                                                  | kbit/s             |  |  |  |

| Data coding          | READ                              | Manchester or Bi-Phase                               |                    |  |  |  |

|                      | WRITE                             | Binary Pulse Length Modulation (BPLM)                |                    |  |  |  |

| Data transmissio     | n mode                            | Half-Duplex                                          |                    |  |  |  |

| Modulation           |                                   | Amplitude Shift Keying (ASK)                         |                    |  |  |  |

| Identifier (serial r | number and product type ID)       | 32                                                   | bit                |  |  |  |

| Secret Key           |                                   | 96                                                   | bit                |  |  |  |

| Authentication tir   | ne (typ)                          | 53                                                   | ms                 |  |  |  |

| Special Features     | s, Note 1 • Ciphered mutual authe | entication and data transmission, according to HT2 S | Security Algorithm |  |  |  |

|                      | Functional compatible             | with Security Transponder PCF7938XA.                 |                    |  |  |  |

Note

1. Custom features may be implemented by a corresponding user application code.

# **RISC Operation**

| PA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RAMETER                          | VALUE        | UNIT |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------|------|

| Operating supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | e (RISC)                         | 2.1 - 3.6    | V    |

| Power-down current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                  | 100          | nA   |

| ROM (System Code Me                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | emory)                           | 4 K          | Byte |

| E-ROM (Application Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | de Memory)                       | 16 K (E-ROM) | Byte |

| RAM (user)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                  | 192          | Byte |

| EEPROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                  | 512          | Byte |

| General purpose I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                  | 7 (TSSOP20)  |      |

| Operating speed, as de                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | rived from on-chip RC oscillator | 0.125 – 2    | MHz  |

| Operating speed, as derived from on-chip RC oscillator       0.125 - 2       MH2         Special Features       • EEPROM Erase/Write over full operating voltage range (2.1 to 3.6 V)       • Capable to derive power supply from Contactless LF Interface         • Full control over Contactless LF Interface       • Full control over Contactless LF Interface         • Programmable voltage comparator for battery voltage monitoring       • PWM generation         • Watchdog timer       • Up to seven dedicated button inputs         • 32 bit serial number and product type identifier |                                  |              |      |

| <ul> <li>Supports Standard HT2 or HT3 security algorithm (Secret Key 48 or 96 bit)</li> <li>Supports Pseudo Random Number generation (Rolling Code)</li> <li>Compatible with product family e.g. PCF7938XA, PCF7x41XTT, PCF7952XTT, PCF7953XT</li> </ul>                                                                                                                                                                                                                                                                                                                                           |                                  |              |      |

# PCF7961XTT

# **UHF Transmitter**

| P                        | ARAMETER VALUE                                                                                                                                                                                          | UNIT |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Operating supply voltage | ge 2.1 – 3.6                                                                                                                                                                                            | V    |

| Supply current (434 MI   | Hz)                                                                                                                                                                                                     |      |

| TRANSMIT m               | ode 9.8                                                                                                                                                                                                 | mA   |

| LOCKED mod               | le 1.5                                                                                                                                                                                                  | mA   |

| Carrier frequency        | 315 or 434                                                                                                                                                                                              | MHz  |

| Output power (434 MH     | z) 9                                                                                                                                                                                                    | dBm  |

| Special Features         | <ul> <li>Programmable XTAL load capacitance</li> <li>Programmable FSK modulation characteristics</li> <li>Programmable output amplitude</li> <li>Programmable ASK modulation characteristics</li> </ul> |      |

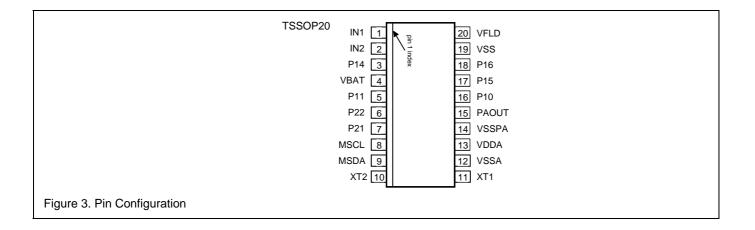

# 7 PINNING

| FUNCTION | FUNCTION DESCRIPTION                                                                                                      |    | NOTE |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------|----|------|--|--|

|          |                                                                                                                           |    |      |  |  |

| IN1      | Input, Transponder Interface (Coil)                                                                                       | 1  |      |  |  |

| IN2      | IN2 Input, Transponder Interface (Coil)                                                                                   |    |      |  |  |

| P14      | General purpose I/O with switch able internal pull-up and Wake Up sense                                                   | 3  |      |  |  |

| VBAT     | Battery Supply Voltage (Battery pos. Terminal)                                                                            | 4  |      |  |  |

| P11      | General purpose I/O with internal pull-up and Wake Up sense                                                               | 5  |      |  |  |

| P22      | General purpose I/O, Wake Up sense and Timer 1 compare output (PWM)                                                       | 6  |      |  |  |

| P21      | General purpose I/O, with switch able internal pull-up, Wake Up sense and Timer/Counter 1 Capture input / Interrupt input | 7  |      |  |  |

| MSCL     | ROM Monitor Serial Clock Output                                                                                           | 8  | 1    |  |  |

| MSDA     | MSDA ROM Monitor Serial Data with internal pull-up                                                                        |    | 1    |  |  |

| XT2      | XTAL Oscillator                                                                                                           | 10 |      |  |  |

| XT1      | XTAL Oscillator                                                                                                           | 11 |      |  |  |

| VSSA     | Transmitter analogue ground                                                                                               | 12 |      |  |  |

| VDDA     | Transmitter analogue supply voltage                                                                                       | 13 |      |  |  |

| VSSPA    | Transmitter power amplifier ground                                                                                        | 14 |      |  |  |

| PAOUT    | Transmitter power amplifier output                                                                                        | 15 |      |  |  |

| P10      | General purpose I/O with internal pull-up and Wake Up sense                                                               | 16 |      |  |  |

| P15      | General purpose I/O, external clock input and Wake Up sense                                                               | 17 |      |  |  |

| P16      | General purpose I/O, Voltage comparator input and Wake Up sense                                                           |    |      |  |  |

| VSS      | Common Ground (Battery neg. Terminal)                                                                                     | 19 |      |  |  |

| VFLD     | Rectified LF Field Supply Voltage                                                                                         | 20 |      |  |  |

### Note

1. MSCL is an open drain output in PUSH configuration and must be left unconnected in the application. During in-circuit flashing or debugging an external pull down resistor is required for proper operation. MSDA features an on-chip pull-up to VBAT. MSDA may be left open or terminated to VBAT, as desired. For field use, the device shall be configured for PROTECTED mode, after the application code has been flashed, see section 12.

# SMART

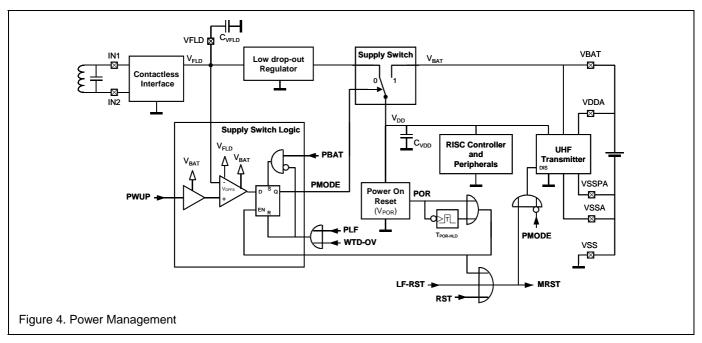

# 8 POWER MANAGEMENT DESCRIPTION

The PCF7961X features a versatile Power Management enabling the device to derive its power supply from either the external battery or the LF Field, as selected by the onchip Supply Switch, Figure 4. The UHF Transmitter is operational only, if the device supply is derived from the battery. However, the XTAL Oscillator is operational in any case, see also section 21.1.

Determining the appropriate supply configuration and hence Supply Switch state, is accomplished by means of the Supply Switch Logic and the ROM implemented device BOOT sequence. During device power-up the Supply Switch Logic will evaluate the supply condition and set the Supply Switch accordingly. Subsequently, the RISC Controller will commence program execution, starting with the BOOT sequence, which under certain conditions will change the Supply Switch state, hence change the supply configuration, before the application program is executed finally. Such condition may apply, in case an LF Field and button press is detected at the same time.

Each supply configuration corresponds to a certain device operating mode, referred to as BATTERY, TRANSPONDER or POWER-OFF Mode. The device is supplied either from an external battery (BATTERY Mode) or from the LF Field (TRANSPONDER MODE) or virtually consumes no power at all (POWER-OFF Mode).

In case the device is supplied from the rectified LF Field (pin VFLD), an on-chip low dropout voltage regulator is

operational, adjusting the voltage to fit the internal chip supply voltage specification ( $V_{DD}$ ).

The Power Management features a set of control bits and flags to influence the supply condition and program execution as desired.

In any case, a Power On Reset circuitry monitors the device supply voltage ( $V_{DD}$ ), forcing the device into the reset state (MRST), in case the chip supply voltage drops below the Power On Reset threshold voltage. The Power On Reset circuitry is able to detect voltage dips as short as 10 us and features a hysteresis of typical 80 mV. Once triggered, the Power On Reset will be prolonged ( $t_{POR-HLD}$ ) by a corresponding mono-flop, to ensure proper device start-up. A device reset is also generated in case an LF Field Detect is detected (LF-RST), provided the LF Field Detect circuitry is configured accordingly, see also section 9.4. Moreover, a device reset may be forced upon instruction, by triggering the control bit RST

After battery power-up, the device enters either POWER-OFF or BATTERY Mode. Thus, the application program cannot detect, that the battery has been changed or has been inserted, see also section 22.9.

### Note

<sup>1.</sup> For information only, the on-chip capacitor  $C_{\text{VDD}}$  yields 2nF

### 8.1 Supply Switch Logic

The Supply Logic selects the appropriate Supply Switch state during device power-up. It evaluates the supply condition and responds to a Port Wake-Up (PWUP) event or LF Wake-Up event, see Figure 4.

The Supply Switch is controlled by a flip-flop that is forced into transparent state, whenever the device supply voltage  $(V_{DD})$  stays below the Power On Reset threshold. By default the device is configured for LF Field supply (PMODE = 0), even if no LF Field is present, meaning that the voltage at pin VFLD is zero. This is achieved by means of a small offset voltage introduced at the negative comparator input.

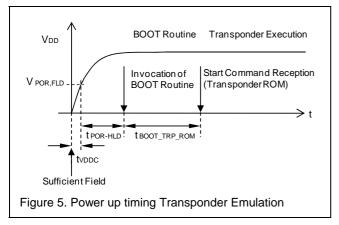

Regardless of the supply condition, once the supply voltage  $(V_{DD})$  exceeds the Power On Reset threshold voltage  $(V_{POR,BAT}$  respectively  $V_{POR,FLD}$ ), POR becomes low. After a short delay ( $t_{POR,HLD}$ ), the flip-flop is forced into latch state freezing the supply switch state and the RISC Controller becomes operational. Program execution commences starting with the BOOT Routine, before the application Program or Transponder Emulation is being invoked (see Figure 5 and section 14).

Altering the supply condition, hence state of the supply switch, during RISC operation is feasible upon instruction only. Latter one may be desired under certain conditions, e.g. when an LF Field is being detected, while battery supply has been utilized so far. To alter the supply condition, the flip-flop state may be changed by triggering the control bits PBAT and PLF.

If the Watchdog Timer is allowed to overflow in BATTERY mode, the Supply Switch will be forced to LF Field supply, typical causing a device reset, see also section 11.6.

### Presence of LF Field

In case the LF Interface is fed by a corresponding input signal, due to the presence of an LF Field, it is rectified and charges the capacitor  $C_{VFLD}$ . As the voltage develops at pin

VFLD (V<sub>FLD</sub>), the low dropout voltage regulator becomes operational. As soon as the chip supply voltage (V<sub>DD</sub>) exceeds the Power On Reset threshold voltage (V<sub>POR,FLD</sub>), the signal POR becomes low. After a short delay (t<sub>POR,HLD</sub>), the flip-flop is forced into latch state freezing the supply switch state (PMODE = 0). Hence, the device is supplied from the LF Field, regardless of any subsequent Port Wake Up events (button press) and unless changed by the application program.

### Port Wake Up (button press)

In case no LF Field is present and a Port Wake Up condition is applicable, e.g. one of the button input is forced low, the comparator forces the flip-flop into high state (PMODE = 1). Consequently, the device is connected to the battery. As soon as the chip supply voltage ( $V_{DD}$ ) exceeds the Power On Reset threshold voltage ( $V_{POR,BAT}$ ), the signal POR becomes low. After a short delay ( $t_{POR,HLD}$ ), the flip-flop is forced into latch state freezing the state of the supply switch. Hence, the device is supplied from the battery, regardless the voltage that may develop at pin VFLD subsequently.

However, since it is desired to give LF Field supply, hence transponder operation, priority over battery supply, the device will respond to an LF Field detected, by overwriting the flip-flop state and changing the supply condition according to section 9.4.

### Presence of LF Field and Port Wake Up (button press)

In case an LF Field and a Port Wake Up condition, e.g. button press, are present at the same time, LF Field supply is forced by default, since the voltage at VFLD exceeds the battery voltage ( $V_{BAT}$ ) typically. Consequently, the comparator forces the flip-flop into low state. Anyhow, in case of a weak LF Field and higher battery voltage the supply switch may be set for battery supply initially, which subsequently would be changed to LF Field supply by the BOOT routine, provided the LF Field triggered the LF Field Detection circuitry, thus is detected to exceed the LF Field Detect threshold voltage ( $V_{THR,FD}$  respectively  $V_{THR,FD-VIN}$ ). In the latter case, the LF Field can be expected being sufficiently strong to support device operation, see also section 9.4.

### 8.2 Device Operating Modes

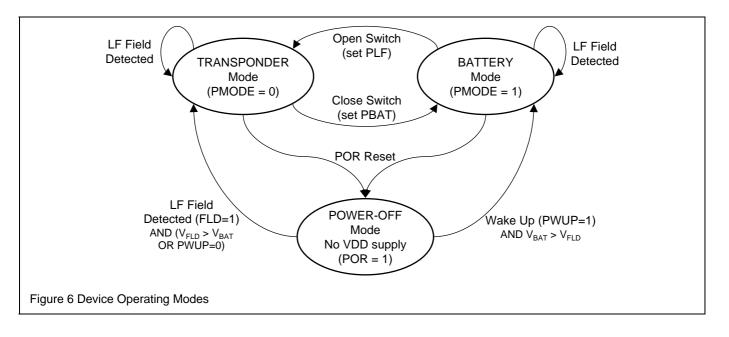

The device resides in one of three modes, POWER-OFF, BATTERY or TRANSPONDER Mode, see Figure 6.

Each mode corresponds to a certain device supply configuration. Hence the device is supplied either from an external battery (BATTERY Mode) or from the LF Field (TRANSPONDER Mode) or virtually consumes no power from the battery at all (POWER-OFF Mode). The device resides in POWER-OFF Mode any time a Power On Reset condition is applicable, either because of a weak supply condition or forced by the application program. The POWER-OFF Mode is terminated, upon a Wake Up event, e.g. presence of an LF Field or Port Wake Up (button press). Once the Supply Switch Logic evaluated the supply condition during device powerup and the BOOT sequence completed, the device will commence execution of the application program in either BATTERY mode or TRANSPONDER mode.

### 8.2.1 POWER-OFF Mode

In POWER-OFF Mode, the internal Supply Switch disconnects the device from the battery (PMODE = 0), making the device to drain virtually no current from the battery. The internal device supply voltage ( $V_{DD}$ ) stays below the power on reset threshold voltage ( $V_{POR,FLD}$ ) and device operation is halted. Only a minimum of circuitry remains operational, like the Power Management and I/O Port circuitry, however, latter one is configured for input mode in any case.

The POWER-OFF Mode is terminated and BATTERY Mode entered, upon a Port Wake Up (WUP = 1), in case

one of the button inputs has been forced low at least (see also section 8.3). Considering an LF Field is present in the same moment, the BOOT sequence will terminate the BATTERY Mode and interrogates the TRANSPONDER Mode instead, provided the LF Field is strong enough and triggered the LF Field Detect circuitry (FLD = 1). Latter one is the case, when the LF Field applied exceeds the LF Field Detect threshold voltage ( $V_{THR,FD}$  resp.  $V_{THR,FD-IN}$ ) (see also section 9.4).

The POWER-OFF Mode is terminated and TRANSPONDER Mode entered, whenever a proper LF Field supply condition is applicable, as evaluated by the Supply Switch Logic, see also section 8.1.

# 8.2.2 BATTERY Mode

In BATTERY Mode, the internal Supply Switch connects the battery with the device supply (PMODE = 1) and powers the device from the external battery.

Device operation is controlled by the RISC and the corresponding program code. Program execution starts with the BOOT sequence before control is passed to the corresponding WARM BOOT vector enabling the application code to be executed (see also section 14).

In case no LF Field is detected while executing the BOOT sequence, control is passed to the WARM BOOT vector BATTERY ( $0000_H$ ) finally. Otherwise, in case the LF Field Detect circuitry is detected being triggered (FLD = 1), the BOOT sequence will terminate the BATTERY Mode and interrogate the TRANSPONDER Mode. This would disconnect the device from the battery and force an LF Field supply condition. Depending on the device configuration, the BOOT sequence immediately invokes the corresponding transponder emulation or directly branches to the WARM BOOT vector TRANSPONDER ( $0010_H$ ) (see also section 11.1.1.2).

Once control has been passed to the corresponding WARM BOOT vector, the application code is responsible to handle and respond to any subsequent events appropriately, e.g. LF Field detected, including transponder invocation.

Upon instruction, the application code may terminate the BATTERY Mode at any time, by clearing the latch PMODE. This is accomplished, by triggering the control bit PLF. As a result, the device supply will be derived from the LF Interface and the subsequent device behavior depends on the supply and Wake Up condition.

In case no LF Field is present, and the device supply drops below the Power On Reset threshold, the device enters POWER-OFF Mode. However, the effects of residual charge at pin VFLD need to be taken into account, in order avoid undesired device operation, see section 22.5. In the moment the device enters POWER-OFF Mode, the Supply Switch Logic will take over device control.

In case an LF Field is present, device operation continues in TRANSPONDER Mode, however, the BOOT sequence is not being executed by default and the application code responsible to take the necessary actions, e.g. transponder invocation.

### 8.2.3 TRANSPONDER Mode

In TRANSPONDER Mode, the internal Supply Switch disconnects the battery from the device supply (PMODE = 0), instead, the internal device supply is derived from the LF Interface, hence the rectified LF Field ( $V_{FLD}$ ).

The device operation is controlled by the RISC and the corresponding program code. Program execution starts with the BOOT sequence before control is possibly passed

to the corresponding WARM BOOT vector (TRANSPONDER, 0010H) enabling the application code to be executed (see also section 14). Depending on the device configuration, the BOOT sequence will immediately invoke the corresponding transponder emulation or branch to the WARM BOOT vector directly (see also section 11.1.1.2).

Once control has been passed to the WARM BOOT vector, the application code is responsible to handle and respond to any subsequent events appropriately, e.g. LF Field detected, including transponder invocation.

Upon instruction, the application code may terminate the TRANSPONDER Mode at any time, hence setting the latch PMODE, by triggering the control bit PBAT. Consequently, the device supply would be derived from the battery subsequently. In case the battery supply does not exceed the Power On Reset threshold, a Power On Reset condition applies. Consequently, the Supply Switch Logic takes device control and forcing the device to resume LF Field supply and eventually to start over again.

The POWER-OFF Mode cannot be entered upon instruction, instead POWER-OFF Mode will be entered as soon as the supply voltage drops below the Power On Reset threshold. However, the effects of residual charge at pin VFLD need to be taken into account, in order avoid undesired operation, see also section 22.5. In the moment the device enters POWER-OFF Mode, the Supply Switch Logic will take over device control.

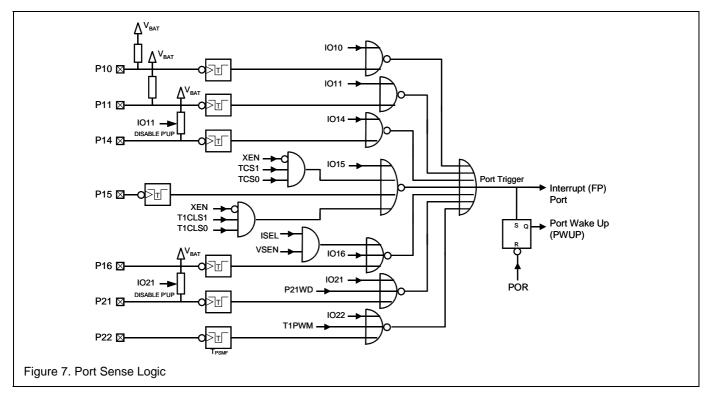

# The Port Sense Logic provides means to wake up the device from POWER-OFF mode or to trigger a corresponding interrupt during program execution, by designated I/O ports (button inputs), according to Figure 7. Upon a high-to-low transition the corresponding port monoflop is triggered and remains set for the specified time $(T_{PSMF})$ , regardless of the subsequent port state. The mono-flop is triggered again upon a high-to-low transition only. Provided the corresponding port is configured for input mode and is not being used in a different context, Port Trigger occurs and a corresponding interrupt request is generated.

When the device resides in POWER-OFF Mode, hence POR (Power On Reset) being high, Port Trigger will set a flip-flop, signaling a Port Wake-Up event. As the RISC Controller resides in Power On Reset state, the Port Interrupt is not being detected. The Supply Switch Logic monitors the state of this flip-flop and will respond to the Port Wake-Up event accordingly, see section 8.1.

The Port Wake Up flip-flop is cleared in the moment the device Power On Reset (POR) vanishes, e.g. as soon as the power-on reset circuitry detects a valid operating voltage, causing the device to commence program execution. Subsequent Port Trigger events, e.g. possibly caused by button bouncing, will be handled as Port Interrupts and the application program shall respond as desired.

# PCF7961XTT

In any case, Port Trigger is supported only, if the designated ports are configured for input mode, hence the corresponding port direction control bit is cleared (IOxx), see section 11.7. Further, the ports must not be used in a different context, possibly overruling the port direction control bit. E.g. P15 as external Timer Counter clock input, see section 11.4 respectively section 11.5; P16 as external Voltage Comparator input, see section 11.9, P21 as Timer 1 Capture input respectively P22 as Timer 1 Pulse Width Modulator output, see section 11.5.

While the device resides in POWER-OFF mode, any of the above mentioned ports generates a Port Wake Up event, because the I/O port are in any case forced into input mode and the Wake Up feature cannot be disabled. In order to avoid unintended device Wake Up, special care is required, when using one of the above ports as an ordinary I/O, see section 22.7.

In any case, it is necessary to establish static non-floating conditions in port input mode, in order to avoid an undesired quiescent current to be drawn from the battery. As the ports are falling edge sensitive, both, pull-up or pulldown measures are allowed to define the static level. Please note that P10 and P11 already feature an on-chip pull-up and Port P14 and P21 an on-chip pull-up that is active only, when the port operates in input mode.

After battery power-up, the device either enters POWER-OFF or BATTERY Mode. Thus, the application program cannot detect, that the battery has been changed or has been inserted, see also section 22.9.

### 8.4 Power Management Control Register

The Power Management features a set of control bits and flags to influence device operation, arranged in the Power Control register, PCON, that is located in the SFR space of the data memory, see Table 1.

Table 1 Power Control Register, PCON

|                   | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1   | bit 0 |

|-------------------|-------|-------|-------|-------|-------|-------|---------|-------|

|                   | NMI   | Х     | FLD   | PMODE | RST   | PBAT  | PLF     | IDLE  |

|                   | R/W   | W0    | R     | R     | R0/W1 | R0/W1 | R0/W1   | R0/W  |

| Note Address = 26 |       |       |       |       |       |       | s = 26H |       |

- 1. Bits marked 'X' are not connected and reserved for future use. Any read operation yields an undefined result. For future compatibility, any write operation should assign a '0'.

- RST, PBAT, PLF and IDLE provide a trigger signal for the corresponding circuitry. Any read operation yields zero as result.

- 3. PBAT and PLF must not be set to '1' simultaneously.

- 4. RST must not be set to '1' simultaneously with PBAT or PLF.

### FLD, Field Detected

The flag FLD signals the presence of an LF Field by monitoring the rectified LF Field supply. If latter one exceeds the LF Field Detect threshold voltage ( $V_{THR,FD}$  respectively  $V_{THR,FD-IN}$ ) FLD is set, otherwise it is cleared, see also section 9.4.

### PMODE, Power Mode

The flag PMODE signals the current state of the Supply Switch, hence, applicable supply condition, according to Table 2.

Table 2 Power Modes

| PMODE | Supply Condition | Note |

|-------|------------------|------|

| 0     | LF Field supply  |      |

| 1     | Battery supply   |      |

The state of PMODE cannot be altered directly. Instead, indirect control is provided by the control bits PBAT and PLF.

### **PBAT**, Power from Battery

The control bit PBAT provides means to force device supply from battery. Any access that writes a '1' to PBAT will set the Supply Switch accordingly (PMODE = 1). However, PLF must not be set in the same moment.

In any case, when changing the supply condition, the application program shall ensure that the new supply condition is sufficient to supply the device and shall force the device operating current to a minimum during the transition. Otherwise, must be aware of an unexpected Power On Reset event.

# PLF, Power from LF Field

The control bit PLF provides means to force device supply from the LF Field. Any access that writes a '1' to PLF will set the Supply Switch accordingly (PMODE = 0).

In any case, when changing the supply condition, the application program shall ensure that the new supply condition is sufficient to supply the device and shall force the device operating current to a minimum during the transition. Otherwise, must be aware of an unexpected Power On Reset event. It is recommended to use the corresponding ROM library function (PM\_ENABLE\_LF), see section 23.

### **RST, RESET device**

The control bit RST provides means to immediately reset the entire device, causing the device to initialize all Special Function Register to their corresponding reset value and to invoke the boot sequence. The Supply Switch, hence supply condition (PMODE), is not affected directly by the reset, however, will eventually be modified during the boot sequence (see section 14).

This feature is of convenient use, in case an LF Field is being detected, in order to invoke the transponder emulation via the BOOT sequence.

### NMI, Non Maskable Interrupt control

The control bit NMI provides means to configure the device behavior upon detection of an LF Field (FLD = 1), according to Table 3.

Table 3 NMI Control

| NMI | Low to High transition of FLD              | Note |

|-----|--------------------------------------------|------|

| 0   | Trigger device reset                       |      |

| 1   | Trigger NMI (Non Maskable Interrupt, INT0) |      |

In case NMI is cleared, a low to high transition of FLD will reset the entire device, causing the device to initialize all SFR to their corresponding reset value and to invoke the boot sequence. The Supply Switch, hence supply condition (PMODE), is not affected directly by the reset, however, will eventually be modified during the boot sequence (see section 14).

In case NMI is set, the Non Maskable Interrupt, NMI, will be triggered and the corresponding interrupt service routine will be invoked. This feature allows to protect "critical" sections of the application program from being terminated by a reset due to the detection of an LF Field, see also section 22.8.

After a device Power On Reset, the NMI bit is cleared, and resets will be generated upon each LOW-to-HIGH transition of FLD.

# IDLE, IDLE Mode

The control bit IDLE, provides means to force the RISC Controller into IDLE mode. Any access that writes a '1' to IDLE will cause the device to halt program execution after completion of the corresponding instruction, by inhibiting the CPU clock. However, the system clock and all peripherals stay operational. The IDLE mode terminates and program execution is resumed upon a corresponding event, see Interrupt System and IDLE Control, section 11.2.5.

# 9 CONTACTLESS INTERFACE DESCRIPTION

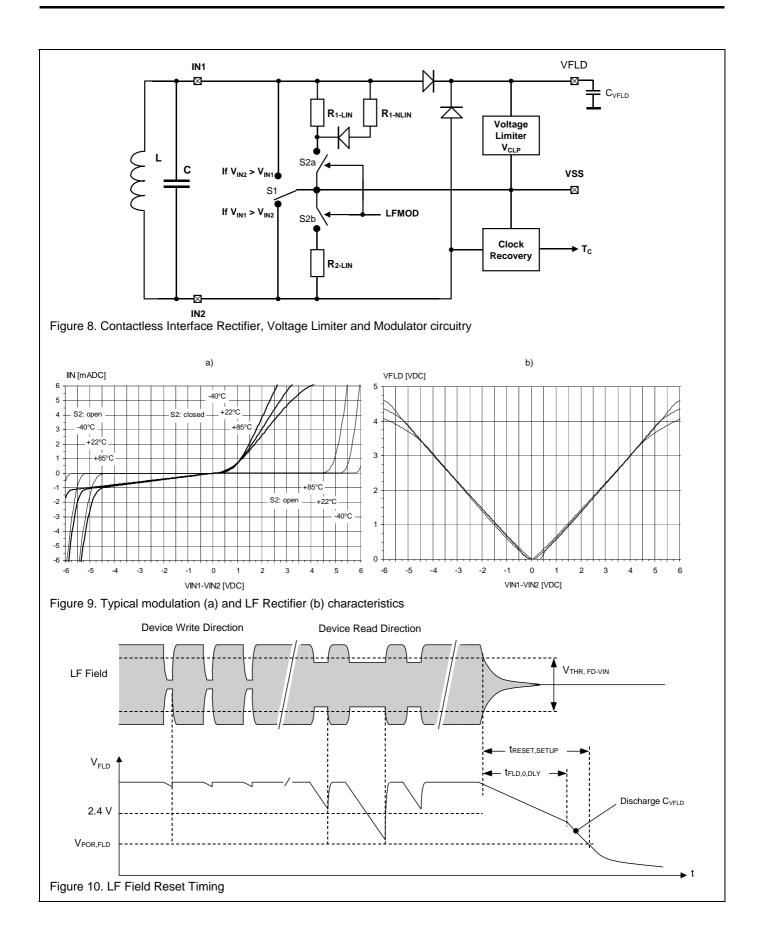

The Contactless Interface provides the means to utilize the PCF7961X as a contactless transponder, capable to derive its power supply and system clock by inductive coupling to an LF Field generated by a corresponding base station. Further, to utilize the same LF Field to receive data from and transmit data to the base station under control of the RISC Controller. An external LC resonant circuit needs to be connected to the coil inputs (IN1 and IN2) of the Contactless Interface, see Figure 8.

Independent from the device operating mode, the Contactless Interface is capable to detect the presence of an LF Field and provides a corresponding signal to Wake Up the device from POWER-OFF mode or to interrupt device operation.

The PCF7961X features build-in means to emulate the NXP transponder family PCF 7938XA, that may be extended by user programmed functions. Please consult the corresponding ROM Library description (see section 23).

The Contactless Interface comprises an LF Rectifier, Voltage Limiter, LF Field Detection, Modulator, Demodulator and Clock Recovery circuitry, see Figure 8.

# 9.1 LF Rectifier and Voltage Limiter

The LF Rectifier operates in full-bridge configuration, charging an external capacitor connected to pin VFLD. A shunt Voltage Limiter is provided to ensure that the voltage at pin VFLD does not exceed the specification. In any case, the interface input current must not exceed the specified limits. The rectifier characteristics are shown in Figure 9b.

The data communication with the device employs Amplitude Shift Keying (ASK) of the LF Field. The modulation duration and LF Field strength must be chosen such that the rectified supply voltage stays above the Power On Reset threshold during the LF Field low condition, see Figure 10.

In case the LF Field is low for a certain duration or switched off, the device will generate a Power On Reset after the specified time ( $t_{RESET,SETUP}$ ), which is desired, in order to provide means to force a device reset during contactless operation, see Figure 10.

# 9.2 Modulator

The Contactless Interface utilizes absorption modulation of the LF Field to send data to the base station. The modulation timing is fully determined by the RISC Controller operating the node LFMOD accordingly.

Absorption modulation is accomplished by applying an additional load (S2 closed) across the coil inputs. The absorption modulation characteristics depend on the source impedance of the external resonance circuit, the modulation load impedance ( $R_{1-LIN}$ ,  $R_{1-NLIN}$  and  $R_{2-LIN}$ ), the Voltage Limiter and the internal power consumption of the device. The applied load (S2) is different for each of the two half waves of the carrier, due to clock recovery reasons. The typical modulation characteristics are shown in Figure 9a.

A dedicated Digital Modulator circuit is provided to easily implement Manchester coding, see section 11.8.

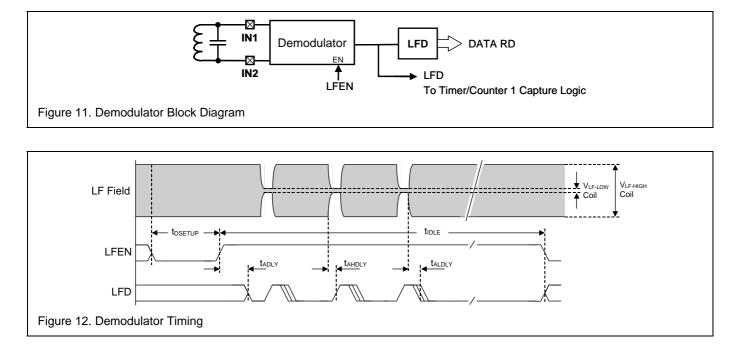

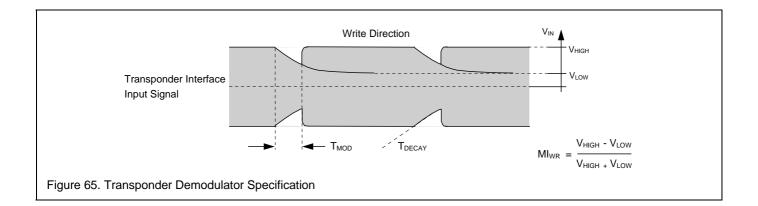

# 9.3 Demodulator

The Contactless Interface utilizes On-Off-Keying (OOK) of the LF Field to receive data from the base station. The demodulator circuitry has been designed to fit the modulation characteristics as implemented by the NXP Transponder PCF7938XA. The Demodulator senses the differential voltage across the coil inputs (pin IN1 and IN2) and signals a corresponding LF Field LOW condition by means of the control bit LFD, see Figure 11 and Figure 12.

Once enabled by the control bit LFEN, the demodulator freezes the internal demodulator threshold and is operational after a short settling time  $(t_{ADLY})$ . The demodulator is designed for temporary operation only and provides its specified operation for a certain duration  $(t_{IDLE})$  only. After that, its characteristics are undefined and it needs to be disabled for a certain time  $(t_{DSETUP})$  before it is enabled again, in order to refresh the demodulator threshold. Hence, data reception as a string is limited accordingly. In any case, the Demodulator signals the LF Field LOW condition only, and the RISC Controller needs to decode the data string bit by bit subsequently. For this reasons, the control bit LFD is also routed to the Timer/Counter 1 Capture Logic, in order to support timer based decoding of the serial data string, see also 11.5.

The demodulator output (LFD) may bounce during the LF Field LOW to HIGH transition, and it is recommended to trigger the Timer/Counter 1 Capture Logic by the rising edge of the demodulator output (LFD).

The Demodulator control bits are arranged in the Demodulator Control register, DEMCON, that is located in the SFR space of the data memory, see Table 4.

# Table 4 LF Demodulator Register, DEMCON

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| LFD   | Х     | Х     | Х     | Х     | Х     | Х     | LFEN  |

| R     | W0    | W0    | W0    | W0    | W0    | W0    | R/W   |

Address = 1CH

Bits marked 'X' are not connected and reserved for future use. Any read operation yields an undefined result. For future compatibility, any write operation should assign a '0'.

### LFEN, LF Demodulator Enable

Note

When the control bit LFEN is set, the Demodulator is enabled, otherwise disabled. In the moment the Demodulator is forced from disabled to enabled state, it will set and freeze its demodulator threshold and be operational for the specified time ( $t_{\text{IDLE}}$ ). After that time, its operation is not specified. During a LF Field modulation phase the demodulator shall be disabled

### LFD, LF Demodulator Data

When the demodulator detects a LF Field LOW modulation, LFD is set, otherwise it is cleared, provided the Demodulator is enabled and the IDLE time did not elapse ( $t_{\text{IDLE}}$ ). While the demodulator is disabled, the LFD bit yields a one.

During Demodulator settling  $(t_{ADLY})$  LFD is undefined and may change randomly, which needs to be taken into account, e.g. by disabling the Timer/Counter 1.

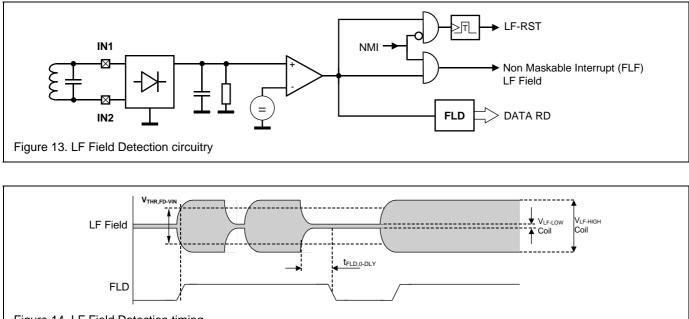

# 9.4 LF Field Detection

Independent of the actual device operating state, the Contactless Interface is capable to detect the presence of an LF Field, in order to Wake Up the device from POWER-OFF mode or to interrupt device operation, see Figure 13 and Figure 14.

The circuit comprises of an independent envelope detector that senses the differential voltage across the coil inputs (pin IN1 and IN2) followed by a comparator. The LF Field envelope is compared with a certain threshold, which by design is greater than the power-on reset threshold ( $V_{POR,FLD}$ ), forming the Field Detect flag, FLD. Latter one turns high, when the LF Field exceeds the Field Detect threshold ( $V_{THR,FD-VIN}$ ) and it may be tested by the RISC Controller when desired.

The envelope detector integration constant is chosen such that the data transmission write pulse  $(T_{WRP})$ , during transponder data reception, does not toggle the Field Detect flag. Instead the LF Field needs to be off for a certain time  $(t_{FLD,0-DLY})$  before FLD becomes low, see Figure 14.

Whenever FLD turns low, certain device circuitry will be activated (e.g. RC Oscillator), in order to consume the charge stored in the external capacitor at pin VFLD and as a result, to safely generate a device reset, satisfying the LF Field Power On Reset setup time specification ( $t_{RESET,SETUP}$ ), see also section 9.1. In addition, ensures that the voltage at pin VFLD is low enough ( $V_{FLD} < V_{BAT}$ ), to allow a Port Wake-Up to interrogate the BATTERY Mode.

Depending of the Power Management configuration, a lowto-high transition of Field Detect (FLD) causes either a device reset (LF-RST) or the invocation of the non maskable interrupt (LF Field).

In case NMI is cleared, a low to high transition of FLD will reset the entire device, causing the device to initialize all SFR to their corresponding reset value and to invoke the boot sequence. Otherwise, in case NMI is set, the Non Maskable Interrupt, NMI, will be triggered and the corresponding interrupt service routine will be invoked. This feature allows to protect "critical" sections of the application program from being terminated by a reset due to the detection of an LF Field, see also section 22.8.

In case invocation of the non maskable interrupt is selected and considered operating from battery supply (BATTERY Mode) it is up to the application program, whether to force a LF Field supply condition (TRANSPONDER Mode) or not. However, FLD being set is no guarantee that the available LF Field is sufficient to power the device. A device Power On Reset may eventually occur in case of a weak LF Field, which needs to be taken into account once the LF Field supply condition is forced.

# FLD, Field Detected

The flag FLD signals the presence of an LF Field, by monitoring the rectified LF Field supply. In case it exceeds the LF Field Detect threshold voltage ( $V_{THR,FD}$  resp.  $V_{THR,FD-IN}$ ) FLD is set, otherwise it is cleared, The Field Detect flag is located in the Power Management Control register, PCON, see section 8.3.

Figure 14. LF Field Detection timing

# SMART

# **10 RISC CONTROLLER DESCRIPTION**

The PCF7961X is powered by NXP's 2<sup>nd</sup> generation low power 8-Bit MICRO RISC KERNEL (MRK II) to control device operation in BATTERY and TRANSPONDER Mode.

The MRK II utilizes a Harvard architecture featuring an 8 bit ALU and 16 bit instruction width. Due to the two stage pipeline concept, instructions virtually execute in a single clock cycle, resulting in an ultra low power consumption. The applicable instruction set is downward compatible to the MRKI Family of products, featuring a number of extended addressing modes and architectural enhancements. For a general description of the MRK II core, please refer to the specification MRK II Family, Architecture and Instruction Set, see section 23. However, the PCF7961X specific implementation of the MRK II core is described below.

# **10.1 Application Code Memory**

The PCF7961 provides 16 kByte of Application Code, Each instruction consists of 16 bit and thus occupies two bytes, see Figure 15.

After a device reset, program execution starts with the BOOT routine and subsequently continues with the Application Code, commencing at the corresponding WARM BOOT vector (see section 14). In BATTERY Mode, execution starts from location 0000H, in TRANSPONDER Mode from location 0010H, provided the Transponder Emulation is disabled (TEN = 0, see section 11.1.1.2)..

Transponder Sub Command handling and unresolved SYS calls feature dedicated vectors that are accessed in the corresponding event.

The PCF7961X features 5 interrupt vectors. Each vector is assigned to a fixed location in the memory. INT 5 and INT 6 are reserved for future use.

Interrupt vectors INT 1 to INT 4 can independently be enabled or disabled. If an interrupt is enabled, it causes the RISC controller to perform a CALL operation to the corresponding location, where execution of the Interrupt Service Routine, ISR, commences. E.g. in case of an INT 2 interrupt (Timer 0 Overflow) program execution would commence at memory location 0006H. A JMP instruction needs to be placed at the corresponding location, in order to redirect program execution to the final location of the ISR (interrupt service routine). It is recommended to place a RETI instruction at all interrupt vectors not used.

Interrupt vector INT0 is not maskable (NMI, not maskable interrupt). It is always executed immediately if a request is generated. The behavior of INT0 can be configured according to section 9.4.

PC (byte addr.) 0000H WARM BOOT (BATTERY) 0002H INT 0 (NMI), LF Field 0004H INT 1, Port 0006H INT 2, Timer 0 INT 3, Timer 1 Compare 0008H 000AH INT 4, Timer 1 Capture 000CH INT 5, reserved 000EH INT 6, reserved WARM BOOT (TRANSPONDER) 0010H 0012H Sub Command Detected 0014H Unresolved SYS Call 0016H Program Memory ROM Program 0FFDH Memory Program ROM reserved 0FFEH Memory E-ROM PCF7961 (4KB) 1FFDH 1FFEH reserved PCF7961 (8KB) 3FFDH 3FFEH reserved PCF7961 (16KB) Figure 15. Application Code Memory

In the case of simultaneous interrupts, the interrupt with the

lowest vector address is executed first.

Note

1. The upper two bytes are reserved for device configuration purposes in any case and are not available to the application.

# 10.2 System Code Memory

The PCF7961X features 8 kByte of System Code Memory that holds a predefined NXP implemented ROM Library featuring a set of library functions, the Transponder Emulation, the device Boot routine and controls the incircuit Monitor and Download Interface. The System Code Memory is not visible to the application. The ROM Library functions and Transponder Emulation are invoked by a System Call (SYS instruction) that passes control back to the application program, when completed.

The Interrupt System is disabled during execution of system code, including the NMI. Thus, any interrupt request is latched only and execution delayed until control is returned to the application code.

For a detailed description of the ROM Library, please refer to specification PCF7x61X ROM Library, Implementation and Description, see also section 23.

# PCF7961XTT

# **Boot Routine**

The BOOT routine is invoked immediately after a device reset. The BOOT routine configures the device, e.g. determines the supply condition, evaluates device protection flags, invokes transponder emulation modes according to the EEPROM configuration and passes control to the Application Code accordingly, see section 14.

### **ROM Library**

The ROM library features a set of functions to emulate the NXP HT3 transponder, as well as a set of generic functions. The corresponding functions are invoked from the application program by a System Call (SYS instruction). For more detailed usage, please refer to the specification HT3-Transponder-ROM, Implementation and Description (see also section 23).

# In-Circuit Monitor and Download Routine

The in-circuit Monitor and Download Interface provides means for E-ROM and EEPROM initialization and to monitor and manipulate the embedded peripherals in the context of system debugging, employing communication via a two-wire serial interface (MSDA / MSCL), see section 15.

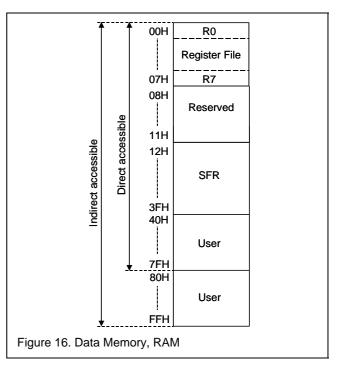

# 10.3 Data Memory

The PCF7961X Data Memory address space is split into a Register File (R0 to R7), reserved space, Special Function Registers (SFR) and 192 byte User RAM, see Figure 16.

The application program may not address the reserved address space from 08H to 11H in order to prevent unintended results.

The SFR space enables I/O from/to the peripherals, the transponder interface and EEPROM as well as control of the interrupt system. The User segment provides RAM for volatile application data and Stack storage. RAM space up to address  $7F_H$  supports direct and indirect addressing, while RAM space beyond  $7F_H$  supports indirect addressing only. For details, refer to the specification MRK II Family, Architecture and Instruction Set, see section 23.

# 11 PERIPHERIAL DESCRIPTION

In order to enable access to the peripherals like the Contactless Interface, the EEPROM as well as to control operation of the Interrupt System Power Management and

Table 5 Special Function Register Summary

UHF Transmitter, a set of Special Function Register, SFR, is provided. Table 5 provides a comprehensive overview of the SFR organization and their corresponding values after a device reset.

| NAME   | DESCRIPTION                | ADDR            | BIT 7 | BIT 6  | BIT 5  | BIT 4 | BIT 3 | BIT 2 | BIT 1  | BIT 0  | RESET<br>VALUE                  |

|--------|----------------------------|-----------------|-------|--------|--------|-------|-------|-------|--------|--------|---------------------------------|

| PSW    | Program Status Word        | 12 <sub>H</sub> | С     | Н      | OV     | Х     | C'    | H'    | OV'    | X'     |                                 |

| SP     | Stack Pointer              | 13 <sub>н</sub> | SP7   | SP6    | SP5    | SP4   | SP3   | SP2   | SP1    |        | $0000000X_{B}$                  |

| SBIT   | Indirect Bit Address       | 14 <sub>H</sub> | MAP   |        |        |       |       | SBIT2 | SBIT1  | SBIT0  |                                 |

| SPTR   | Indirect Byte Address      | 15 <sub>н</sub> | SPTR7 | SPTR6  | SPTR5  | SPTR4 | SPTR3 | SPTR2 | SPTR1  | SPTR0  |                                 |

| IE     | Interrupt Enable           | 16 <sub>н</sub> | EA    |        | EE     | ET1A  | ET1O  | ET0   | EP     |        | $0 \times 0 0 0 0 0 \times_{B}$ |

| IFF    | Interrupt Flag             | 17 <sub>H</sub> |       |        | FE     | FT1A  | FT1O  | FT0   | FP     |        | $XX00000X_B$                    |

| Т0     | Timer/Counter 0            | 18 <sub>H</sub> |       |        |        |       |       |       |        |        |                                 |

| TR0    | Timer/Counter 0 Reload     | 19 <sub>H</sub> |       |        |        |       |       |       |        |        |                                 |

| TCON   | Timer/Counter 0 Control    | 1A <sub>H</sub> |       | TPS2   | TPS1   | TPS0  | TCS1  | TCS0  |        | TRS0   | X00000X0 <sub>b</sub>           |

| WTCON  | Watchdog Timer Control     | 1B <sub>H</sub> |       | WPS2   | WPS1   | WPS0  |       |       |        | WCLR   | $X000XXXX_B$                    |