**DATA SHEET**

# mos integrated circuit $\mu$ PD75P316A

# **4-BIT SINGLE-CHIP MICROCOMPUTER**

#### DESCRIPTION

The  $\mu$ PD75P316A is a product of the  $\mu$ PD75316 with on-chip ROM having been replaced with the one-time PROM or EPROM.

It is most suitable for test production during system development and for production in small amounts since it can operate under the same supply voltage as mask products.

The one-time PROM product is capable of writing only once and is effective for production of many kinds of sets in small quantities and early startup. The EPROM product allows program writing and rewriting, and is therefore suitable for system evaluation. The on-chip RAM has twice the capacity of the  $\mu$ PD75316/75P316, enabling large amounts of data to be processed.

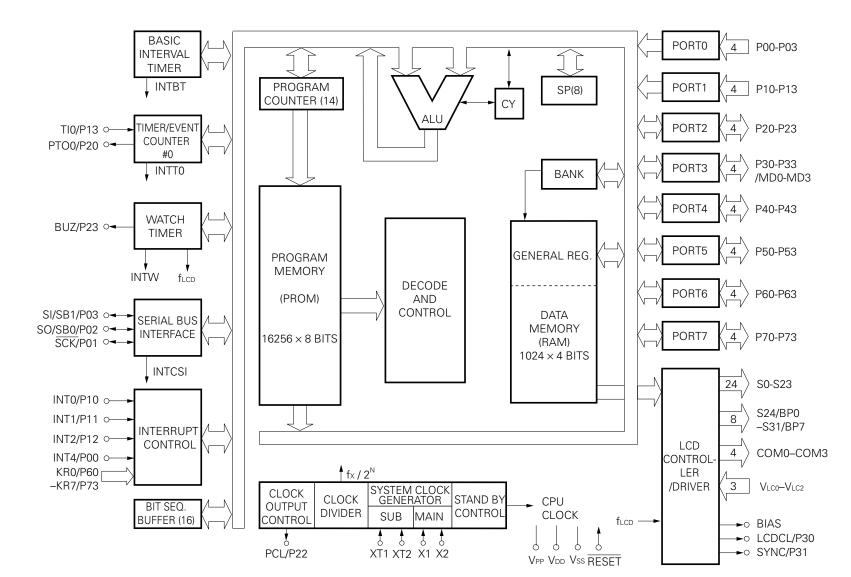

# Details of functions are described in the User's Manual shown below. Be sure to read in design. $\mu$ PD75308 User's Manual : IEM-5016

# FEATURES

- Compatible (excluding mask option) with the mask products

- Memory capacity

- Program memory (PROM): 16256 × 8 bits

- Data memory (RAM) : 1024 × 4 bits

- Low-voltage operation capability: 2.7 to 6.0 V

#### **ORDERING INFORMATION**

| Ordering Code         | Package                               | On-Chip ROM   |  |

|-----------------------|---------------------------------------|---------------|--|

| $\mu$ PD75P316AGF-3B9 | 80-pin plastic QFP (14 $	imes$ 20 mm) | One-time PROM |  |

| $\mu$ PD75P316AK      | 80-pin ceramic WQFN (LCC with window) | EPROM         |  |

#### QUALITY GRADE

| Ordering Code         | Package                               | Quality Grade |  |

|-----------------------|---------------------------------------|---------------|--|

| $\mu$ PD75P316AGF-3B9 | 80-pin plastic QFP (14 $	imes$ 20 mm) | Standard      |  |

| $\mu$ PD75P316AK      | 80-pin ceramic WQFN (LCC with window) | Standard      |  |

Please refer to "Quality grade on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

# In descriptions common to one-time PROM products and EPROM products in this document, the term "PROM" is used.

The information in this document is subject to change without notice.

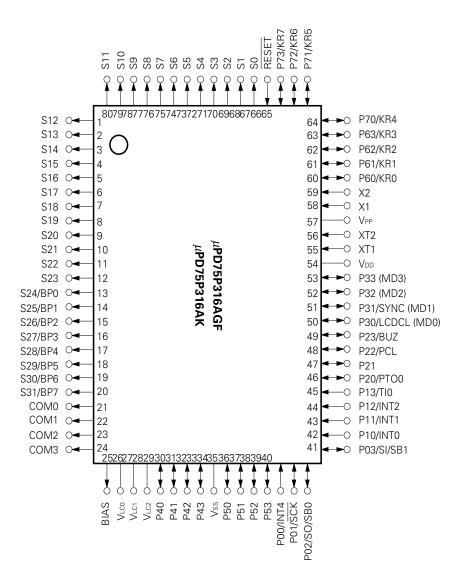

**PIN CONFIGURATION (Top View)**

# CONTENTS

|   | 1. | PIN FUNCTIONS                                   |

|---|----|-------------------------------------------------|

|   |    | 1.1 PORT PINS                                   |

|   |    | 1.2 OTHER PINS                                  |

|   |    | 1.3 PIN INPUT/OUTPUT CIRCUITS                   |

| * |    | 1.4 CAUTION ON USING P00/INT4 PIN AND RESET PIN |

|   | 2. | DIFFERENCES BETWEEN PRODUCTS IN SERIES 11       |

|   | 3. | DATA MEMORY (RAM)13                             |

|   | 4. | PROGRAM MEMORY WRITE AND VERIFY 15              |

|   |    | 4.1 PROGRAM MEMORY WRITE/VERIFY OPERATING MODES |

|   |    | 4.2 PROGRAM MEMORY WRITING PROCEDURE            |

|   |    | 4.3 PROGRAM MEMORY READING PROCEDURE            |

|   |    | 4.4 ERASURE METHOD                              |

|   | 5. | ELECTRICAL SPECIFICATIONS                       |

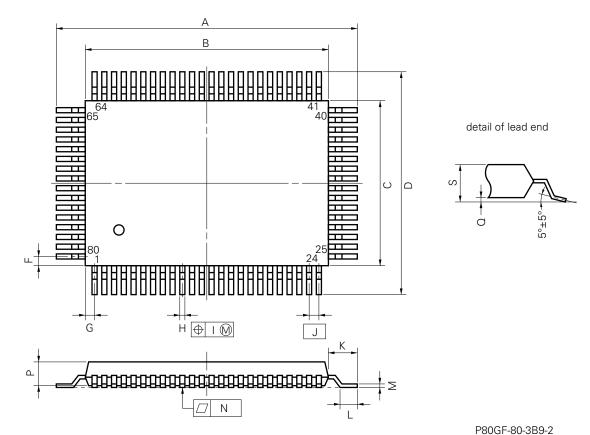

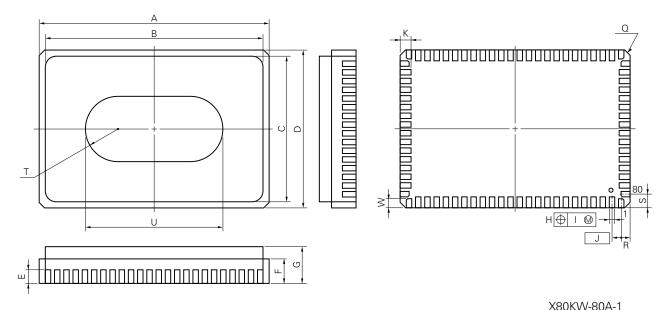

|   | 6. | PACKAGE INFORMATION                             |

|   | 7. | RECOMMENDED SOLDERING CONDITIONS                |

|   | AP | ENDIX A. DEVELOPMENT TOOLS                      |

| * | AP | ENDIX B. RELATED DOCUMENTS                      |

# **1. PIN FUNCTIONS**

# 1.1 PORT PINS (1/2)

| Pin Name              | Input/Output | Du:<br>Functio |     | Function                                                                                                                                     | 8-Bit I/O | Afer Reset     | I/O Circuit<br>Type* <b>1</b> |

|-----------------------|--------------|----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------|-------------------------------|

| P00                   | Input        | IN             | Г4  |                                                                                                                                              |           |                | B                             |

| P01                   | Input/output | SC             | ĸ   | 4-bit input port (PORT0)                                                                                                                     |           |                | (F) - A                       |

| P02                   | Input/output | SO/S           | SB0 | Internal pull-up resistor specification by soft-<br>ware is possible for P01 to P03 as a 3-bit unit.                                         | ×         | Input          | (F) - В                       |

| P03                   | Input/output | SI/S           | B1  |                                                                                                                                              |           |                | M- C                          |

| P10                   |              | IN             | ГО  | With noise elimination circuit                                                                                                               |           |                |                               |

| P11                   |              | IN             | Г1  | 4-bit input port (PORT1)                                                                                                                     |           |                |                               |

| P12                   | Input        | IN             | Г2  | Internal pull-up resistor specification by soft-<br>ware is possible as a 4-bit unit.                                                        | ×         | Input          | (B) - C                       |

| P13                   |              | ті             | 0   |                                                                                                                                              |           |                |                               |

| P20                   |              | PT             | D0  |                                                                                                                                              |           |                |                               |

| P21                   |              | _              | _   | 4-bit input/output port (PORT2)                                                                                                              |           |                |                               |

| P22                   | Input/output | PC             | L   | Internal pull-up resistor specification by soft-<br>ware is possible as a 4-bit unit.                                                        | ×         | Input          | E - B                         |

| P23                   |              | BU             | IZ  |                                                                                                                                              |           |                |                               |

| P30 * <b>2</b>        |              | LCDCL          | MD0 |                                                                                                                                              |           |                |                               |

| P31 * <b>2</b>        |              | SYNC           | MD1 | Programmable 4-bit input/output port (PORT3)<br>Input/output settable bit-wise.                                                              |           |                |                               |

| P32 * <b>2</b>        | Input/output | м              | 02  | Internal pull-up resistor specification by soft-<br>ware is possible as a 4-bit unit.                                                        | ×         | Input          | E - B                         |

| P33 * <b>2</b>        |              | М              | 03  |                                                                                                                                              |           |                |                               |

| P40 to P43* <b>2</b>  | Input/output | _              | -   | N-ch open-drain 4-bit input/output port (PORT<br>4).<br>Data input/output pins for program memory<br>(PROM) write/verify (low-order 4 bits). |           | High impedance | M - A                         |

| P50 to P53 * <b>2</b> | Input/output | _              | -   | N-ch open-drain 4-bit input/output port (PORT 5)<br>Data input/output pins for program memory<br>(PROM) write/verify (high-order 4 bits).    |           | High impedance | M - A                         |

| P60                   |              | KF             | 80  |                                                                                                                                              |           |                |                               |

| P61                   | Innut/cutrut | KF             | 1   | Programmable 4-bit input/output port (PORT6).<br>Input/output settable bit-wise.                                                             |           |                |                               |

| P62                   | Input/output | KF             | 2   | Internal pull-up resistor specification by soft-<br>ware is possible as a 4-bit unit.                                                        |           | Input          | (F) - A                       |

| P63                   |              | KF             | 3   |                                                                                                                                              |           |                |                               |

| P70                   |              | KF             | {4  |                                                                                                                                              | - 0       |                |                               |

| P71                   | Input/cutout | KF             | 15  | 4-bit input/output port (PORT7).                                                                                                             |           | Input          |                               |

| P72                   | Input/output | KF             | 16  | Internal pull-up resistor specification by soft-<br>ware is possible as a 4-bit unit.                                                        |           |                | (F) - A                       |

| P73                   |              | KF             | 7   |                                                                                                                                              |           |                |                               |

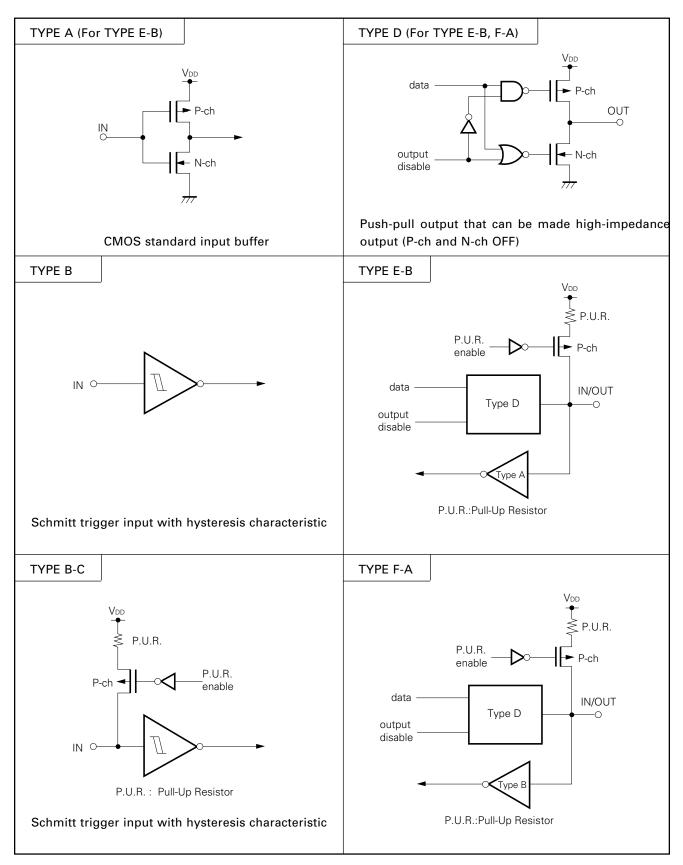

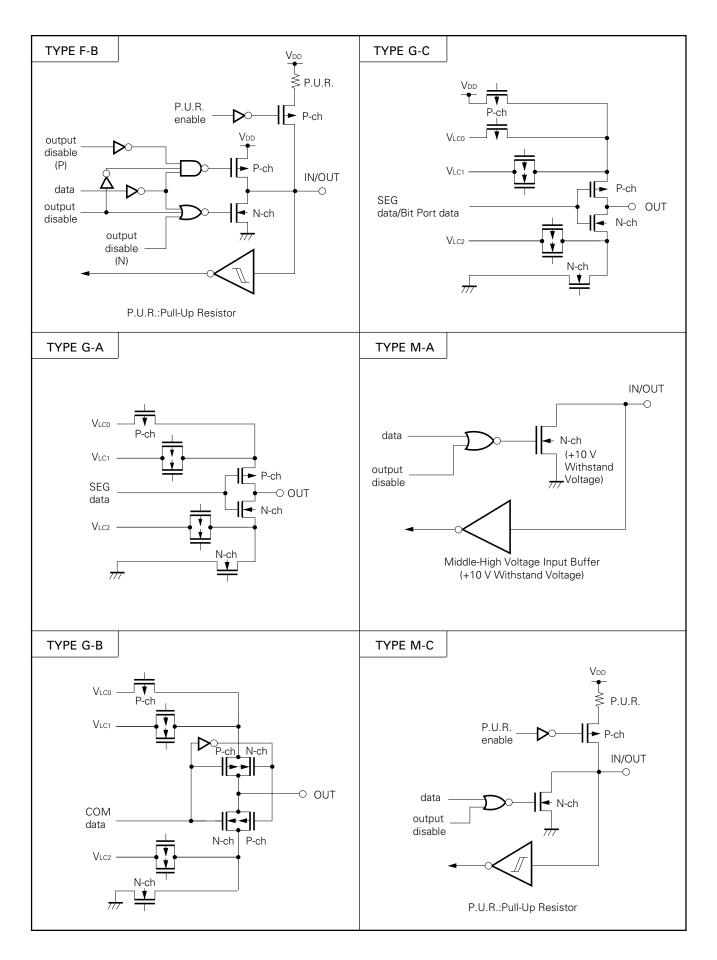

\* 1. (): Indicates a Schmitt-triggered input.

2. Direct LED drive capability.

#### 1.1 PORT PINS (2/2)

| Pin Name | Input/Output | Dual-<br>Function Pin | Function                              | 8-Bit I/O | After Reset | I/O Circuit<br>TYPE |

|----------|--------------|-----------------------|---------------------------------------|-----------|-------------|---------------------|

| BP0      |              | S24                   |                                       |           |             |                     |

| BP1      | Output       | S25                   |                                       |           |             |                     |

| BP2      | Output       | S26                   |                                       |           |             | G - C               |

| BP3      |              | S27                   | 1-bit output port (BIT PORT)          |           | *           |                     |

| BP4      |              | S28                   | Dual-function as segment output pins. | ×         |             |                     |

| BP5      | Output       | S29                   |                                       |           |             |                     |

| BP6      | Output       | S30                   |                                       |           |             |                     |

| BP7      |              | S31                   |                                       |           |             |                     |

\* For BP0 to BP7, VLC1 is selected as the input source. The output level depends on BP0 to BP7 and the VLC1 external circuit, however.

# 1.2 OTHER PINS

| Pin Name       | Input/Output | Dual-<br>Function Pin | Function                                                                                                                                                                                           | After Reset    | I/O Circuit<br>Type * <b>1</b> |

|----------------|--------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------|

| TIO            | Input        | P13                   | External event pulse input pin for timer/event counter.                                                                                                                                            | —              | B - C                          |

| PTO0           | output       | P20                   | Timer/event counter output pin                                                                                                                                                                     | Input          | E - B                          |

| PCL            | Input/output | P22                   | Clock output pin                                                                                                                                                                                   | Input          | E - B                          |

| BUZ            | Input/output | P23                   | Fixed frequency output pin (for buzzer or system clock trimming)                                                                                                                                   | Input          | E - B                          |

| SCK            | Input/output | P01                   | Serial clock input/output pin                                                                                                                                                                      | Input          | (F) - A                        |

| SO/SB0         | Input/output | P02                   | Serial data output pin<br>Serial bus input/output pin                                                                                                                                              | Input          | (F) - В                        |

| SI/SB1         | Input/output | P03                   | Serial data input pin<br>Serial bus input/output pin                                                                                                                                               | Input          | M- C                           |

| INT4           | Input        | P00                   | Edge-detected vectored interrupt input pin (rising or falling edge detection).                                                                                                                     | _              | B                              |

| INT0           | Incut        | P10                   | Edge-detected vectored interrupt input pin (detection edge                                                                                                                                         |                |                                |

| INT1           | Input        | P11                   | selectable)                                                                                                                                                                                        | _              | (B) - C                        |

| INT2           | Input        | P12                   | Edge-detected testable input pin (rising edge detection)                                                                                                                                           | _              | (B) - C                        |

| KR0 to KR3     | Input/output | P60 to P63            | Testable Input/output pins (parallel falling edge detection)                                                                                                                                       | Input          | (F) - A                        |

| KR4 to KR7     | Input/output | P70 to P73            | Testable Input/output pins (parallel falling edge detection)                                                                                                                                       | Input          | (F) - A                        |

| S0 to S23      | Output       | _                     | Segment signal output pins                                                                                                                                                                         | *3             | G - A                          |

| S24 to S31     | Output       | BP0 to 7              | Segment signal output pins                                                                                                                                                                         | *3             | G - C                          |

| COM0 to COM3   | Output       | _                     | Common signal output pins                                                                                                                                                                          | *3             | G - B                          |

| VLC0 to VLC2   | _            | _                     | LCD drive power supply pins                                                                                                                                                                        | _              | _                              |

| BIAS           | _            | _                     | External split cutting output pin                                                                                                                                                                  | High impedance | _                              |

| LCDCL*2        | Input/output | P30                   | External extension driver drive clock output pin                                                                                                                                                   | Input          | E - B                          |

| SYNC* <b>2</b> | Input/output | P31                   | External extension driver synchronization clock output pin                                                                                                                                         | Input          | E - B                          |

| X1, X2         | Input        | _                     | Main system clock oscillation crystal/ceramic connection<br>pins. When an external clock is used, the clock is input to<br>X1 and the inverted clock to X2.                                        | _              | _                              |

| XT1, XT2       | Input        | _                     | Subsystem clock oscillation crystal connection pins<br>When an external clock is used, the clock is input to XT1 and<br>the inverted clock to XT2. XT1 can be used as a 1-bit input<br>(test) pin. |                | _                              |

| RESET          | Input        | _                     | System reset input pin (low-level active).                                                                                                                                                         | _              | B                              |

| MD0 to MD3     | Input/output | P30 to P33            | Mode selection pin for program memory (PROM) write/<br>verify.                                                                                                                                     | Input          | E - B                          |

| Vpp            | _            | _                     | Program voltage application pin for program memory (PROM) write/verify. Connected to $V_{\text{DD}}$ in normal operation. Applies +12.5 V in program memory write/verify.                          | _              | _                              |

| Vdd            | _            | _                     | Positive power supply pin                                                                                                                                                                          | _              | _                              |

| Vss            | _            | _                     | GND potential pin                                                                                                                                                                                  | _              | _                              |

- \* 1. (): Indicates a Schmitt-triggered input.

- 2. Pins provided for future system expansion. Currently used only as pins 30 and 31.

- VLCX shown below can be selected for display outputs.

S0 to S31: VLC1, COM0 to COM2: VLC2, COM3: VLC0

However, display output levels depend on the display output and VLCX external circuit.

# 1.3 PIN INPUT/OUTPUT CIRCUITS

The input/output circuits of each pin of the  $\mu$ PD75P316A are shown by in abbreviated form.

#### $\star$

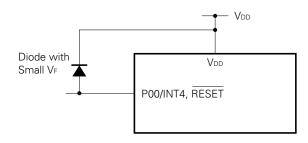

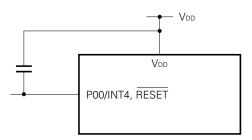

#### 1.4 CAUTION ON USING P00/INT4 PIN AND RESET PIN

The P00/INT4 and RESET pins have a test mode setting function (IC test only) which tests internal operations of the  $\mu$ PD75P316A in addition to those functions given in 1.1 and 1.2.

The test mode is set when voltage greater than VDD is applied to either pin. Therefore, even during normal operation, the test mode is engaged when noise greater than VDD is added, thus causing interference with normal operation.

For example, this problem may occure if the P00/INT4 and RESET pins wiring is too long, causing line noise. To avoid this, try to suppress line noise in wiring. If line noise is still high, try eliminating the noise using the exterior add-on components shown in the Figures below.

Connect a diode with low VF between the VDD and the pin.

#### 2. DIFFERENCES BETWEEN PRODUCTS IN SERIES

The  $\mu$ PD75P316A is a product of the  $\mu$ PD75316 with on-chip mask ROM having been replaced with the one-time PROM or EPROM. If you use PROM for debugging the applied system or trial manufacturing, and proceed to use masked ROM products for mass production, do so only with a full understanding of their differences beforehand.

Also,  $\mu$ PD75P316A functions are an extension of those of the  $\mu$ PD75P316. Table 2-1 shows the differences between the series products. All products have the same functions except as indicated in this table.

For the details of the CPU functions and the built-in hardware, please refer to the  $\mu$ PD75308 User's Manual (IEM-5016).

#### **Table 2-1 Differences between Products in Series**

| F<br>Compariso     | Product Name     | μPD75304/75306/75308                    | μPD75312/75316                            | μPD75304B/75306B/75308B                         | μPD75312B/75316B                                                 | μPD75P308                                                                                     | μPD75P316                         | μPD75P316A                                                                                                  | μPD75P316B* <b>1</b>                                                                    |

|--------------------|------------------|-----------------------------------------|-------------------------------------------|-------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| ROM(× 8 I          | oits)            | Mask ROM<br>4K/6K/8K                    | Mask ROM<br>12K/16K                       | Mask ROM<br>4K/6K/8K                            | Mask ROM<br>12K/16K                                              | One-time PROM,EPROM<br>8K                                                                     | One-time PROM<br>16K              | One-time PROM,EPROM<br>16K                                                                                  | One-time PROM<br>16K                                                                    |

| RAM(× 4 b          | oits)            |                                         | 512                                       |                                                 | 1024                                                             | 5                                                                                             | 12                                | 10                                                                                                          | 24                                                                                      |

| Mask opti          | on               |                                         | Port 4, 5 pull-up re<br>LCD driving power | sistor incorporated<br>supplying split resistor |                                                                  | No                                                                                            |                                   |                                                                                                             |                                                                                         |

| Pin                | No. 50 to 53     |                                         | P30 t                                     | o P33                                           |                                                                  |                                                                                               | P30/MD0                           | to P33/MD3                                                                                                  |                                                                                         |

| connectio          | n No. 57         |                                         | NC                                        |                                                 | IC                                                               |                                                                                               | V                                 | /рр                                                                                                         |                                                                                         |

| Electrical         | specifications   | Masked ROM produ<br>respective data she |                                           | ucts have different currer                      | nt dissipation and op                                            | operating temperature range <b>*2</b> . For details, refer to the electrical specifications o |                                   |                                                                                                             |                                                                                         |

| Power supp         | ly voltage range | 2.7 to                                  | 6.0 V                                     | 2.0 to 6.0 V                                    | 2.0 to 5.5 V                                                     | 5 V ±5 %                                                                                      |                                   | 2.7 to 6.0 V                                                                                                | 2.0 to 5.5 V                                                                            |

| Operating<br>range | temperature      |                                         | -40 to                                    | +85 °C                                          |                                                                  | –10 to                                                                                        | +70 °C                            | –40 to +85 °C                                                                                               | Under<br>investigation                                                                  |

| Package            |                  | • 80-pin plastic QFP (14 × 20)          |                                           |                                                 | • 80-pin plastic<br>OFP (□14)     • 80-pin plastic<br>TQFP (□12) | 80-pin plastic<br>QFP (14 × 20)<br>80-pin ceramic<br>WQFN (LCC with<br>window)                | • 80-pin plastic<br>QFP (14 × 20) | <ul> <li>80-pin plastic<br/>QFP (14 × 20)</li> <li>80-pin ceramic<br/>WQFN (LCC with<br/>window)</li> </ul> | <ul> <li>80 pin plastic<br/>QFP (□14)</li> <li>80 pin plastic<br/>TQFP (□12)</li> </ul> |

| On-chip P          | ROM product      | μPD75P308                               | μPD75P316<br>μPD75P316A                   | μPD75P316A<br>μPD75P316B                        | μPD75P316B                                                       |                                                                                               |                                   | ·                                                                                                           |                                                                                         |

| Others             |                  | Masked ROM produ                        | ucts and PROM prod                        | ucts have different noise                       | endurance limits and                                             | d noise radiation due                                                                         | to differing circuit so           | cales and mask layout                                                                                       | s.                                                                                      |

\* **1**. The  $\mu$ PD75P316B is under development.

12

- **2.** The  $\mu$ PD75P316A is the same as the mask ROM products.

- ★ Note PROM and masked ROM have different noise endurance limits and noise radiation. When considering replacement of masked ROM products after trial manufacturing with PROM products, sufficient evaluation of CS products (not ES products) with masked ROM products should be performed.

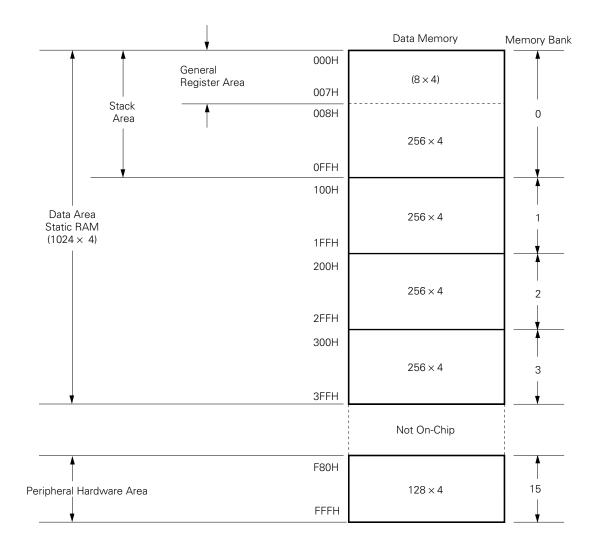

# 3. DATA MEMORY (RAM)

Fig. 3-1 shows the data memory configuration. It consists of a data area and a peripheral hardware area. The data memory consists of memory banks 0 to 3 with each bank consisting of 256 words  $\times$  4 bits. Peripheral hardware has been assigned to the area of memory bank 15.

#### (1) Data area

The data area comprises a static RAM. It is used to store program data and as a subroutine, interrupt execution stack memory. Even if the CPU operation is stopped in the standby mode, it is possible to hold the memory content for a long time by battery backup, etc. The data area is operated by memory manipulation instructions.

The static RAM has been mapped to memory banks 0, 1, 2 and 3 by  $256 \times 4$  bits each. Bank 0 has been mapped as a data area but is also available as a general register area (000H to 007H) and a stack area (000H to 0FFH) (banks 1, 2 and 3 are available only as a data area).

In the static RAM, 1 address consists of 4 bits. It can be operated in units of 8 bits by 8-bit memory manipulation instructions or in bits by bit manipulation instructions, however. In an 8-bit manipulation instruction, an even address should be specified.

#### (a) General register area

The general register area can be operated either by general register operation instructions or by memory manipulation instructions. Up to eight 4-bit registers are available. That part of the 8 general registers which is not used in the program is available as a data area or a stack area.

#### (b) Stack area

The stack area is set by an instruction. It is available as a subroutine execution or interrupt service execution save area.

#### (2) Peripheral hardware area

The peripheral hardware area has been mapped to F80H to FFFH of memory bank 15.

It is operated by memory manipulation instructions just as the static RAM. In the peripheral hardware, however, the operable bit unit differs from one address to another. An address to which peripheral hardware has not been assigned is inaccessible since no data memory is built in.

#### Fig. 3-1 Data Memory Map

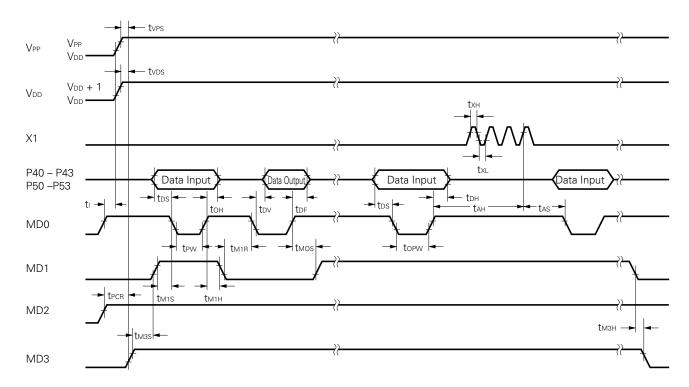

# 4. PROGRAM MEMORY WRITE AND VERIFY

The ROM built into the  $\mu$ PD75P316A is a 16256×8-bit electrically writable one-time PROM. The table below shows the pins used to program this PROM. There is no address input; instead, a method to update the address by the clock input via the X1 pin is adopted.

| Pin Name                                                        | Function                                                                                                                 |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Vpp                                                             | Voltage applecation pin for program memory write/verify (normally $V_{DD}$ potential).                                   |

| X1, X2                                                          | Address update clock inputs for program memory write/<br>verify. Inverse of X1 pin signal is input to X2 pin.            |

| MD0 to MD3                                                      | Operating mode selection pins for program memory write/<br>verify.                                                       |

| P40 to P43 (low-order 4 bits)<br>P50 to P53 (high-order 4 bits) | 8-bit data input/output pins for progrm memory write/<br>verify.                                                         |

| Vdd                                                             | Supply voltage application pin.<br>Applies 2.7 to 6.0 V in normal operation, and 6 V for<br>program memory write/verify. |

Note 1. A lightshield cover film should be applied to the  $\mu$ PD75P316AK provided with an erasure window, except when erasing the EPROM.

2. The one-time PROM version of  $\mu$ PD75P316AGF is not provided with an erasure window, and therefore UV erasure is not possible.

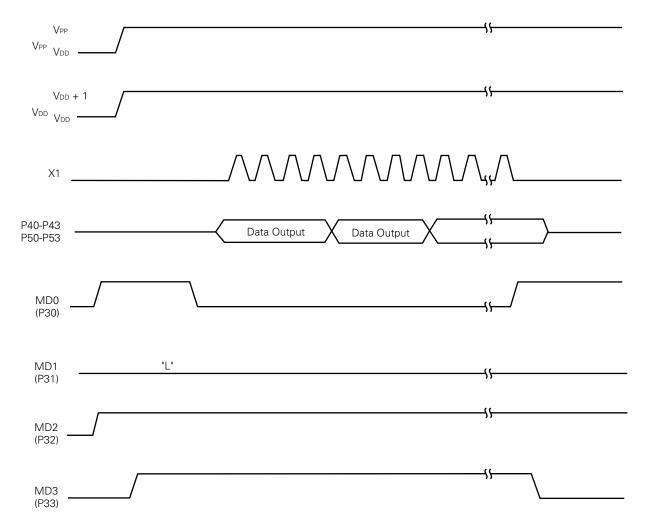

#### 4.1 PROGRAM MEMORY WRITE/VERIFY OPERATING MODES

The  $\mu$ PD75P316A assumes the program memory write/verify mode when +6 V and +12.5 V are applied respectively to the V<sub>DD</sub> and V<sub>PP</sub> pins. The table below shows the operating modes available by the MD0 to MD3 pin setting in this mode. All the remaining pins are at the V<sub>SS</sub> potential by the pull-down resistor.

|         | Operating | Mode S | Setting |     | - Operating Mode |                      |                                   |

|---------|-----------|--------|---------|-----|------------------|----------------------|-----------------------------------|

| Vpp     | Vdd       | MD0    | MD1     | MD2 | MD3              | Operating mode       |                                   |

|         |           |        | H L     | L   | н                | L                    | Program memory address zero-clear |

| 10 5 1/ |           | L      | н       | н   | н                | Write mode           |                                   |

| +12.5 V | +6 V      | L      | L       | н   | Н                | Verify mode          |                                   |

|         |           |        | ×       | Н   | Н                | Program inhibit mode |                                   |

×: L or H

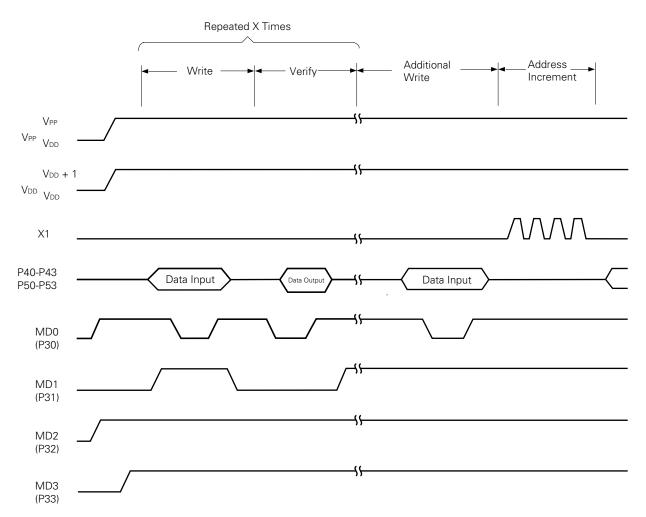

#### 4.2 PROGRAM MEMORY WRITING PROCEDURE

The program memory writing procedure is shown below. High-speed write is possible.

- (1) Pull down a pin which is not used to Vss via the resistor. The X1 pin is at the low level.

- (2) Supply 5 V to the V\_DD and V\_PP pins.

- (3) 10  $\mu$ s wait.

- (4) The program memory address 0 clear mode.

- (5) Supply 6 V and 12.5 V respectively to VDD and VPP.

- (6) The program inhibit mode.

- (7) Write data in the 1-ms write mode.

- (8) The program inhibit mode.

- (9) The verify mode. If written, proceed to (10); if not written, repeat (7) to (9).

- (10) (Number of times written in (7) to (9): X)  $\times$  1-ms additional write.

- (11) The program inhibit mode.

- (12) Update (+1) the program memory address by inputting 4 pulses to the X1 pin.

- (13) Repeat (7) to (12) up to the last address.

- (14) The program memory address 0 clear mode.

- (15) Change the VDD and VPP pins voltage to 5 V.

- (16) Power off.

The diagram below shows the procedure of the above (2) to (12).

#### 4.3 PROGRAM MEMORY READING PROCEDURE

The  $\mu$ PD75P316A can read the content of the program memory in the following procedure. It reads in the verify mode.

- (1) Pull down a pin which is not used to Vss via the resistor. The X1 pin is at the low level.

- (2) Supply 5 V to the VDD and VPP pins.

- (3) 10 µs wait.

- (4) The program memory address 0 clear mode.

- (5) Supply 6 V and 12.5 V respectively to V\_DD and V\_PP.

- (6) The program inhibit mode.

- (7) The verify mode. If clock pulses are input to the X1 pin, data is output sequentially 1 address at a time at the period of inputting 4 pulses.

- (8) The program inhibit mode.

- (9) The program memory address 0 clear mode.

- (10) Change the VDD and VPP pins voltage to 5 V.

- (11) Power off.

The diagram below shows the procedure of the above (2) to (9).

#### 4.4 ERASING METHOD (µPD75P316AK ONLY)

The content of the data programmed in the  $\mu$ PD75P316A is erased as ultraviolet rays are irradiated to the window in the upper part.

The erasable ultraviolet-ray wavelength is about 250 nm.

The dose required for complete erasure is 15 W•s/cm<sup>2</sup> (ultraviolet-ray intensity × erasure time). If a commercially available ultraviolet-ray lamp (wavelength 254 nm, intensity 12 mW/cm<sup>2</sup>) is used, it takes about 15 to 20 minutes to erase.

- Note 1. The content may be erased if exposed to direct sunlight or fluorescent lamp light for a long time. To protect the content, the window in the upper part should be masked with a lightshield cover film. NEC attaches such a lightshield cover film to each UV EPROM product.

- 2. When erasing, the distance between the ultraviolet-ray lamp and the  $\mu$ PD75P316A should be kept normally within 2.5 cm.

- **Remarks** It may take longer to erase if the ultraviolet-ray lamp has deteriorated or if the package window is dirty and so on.

# 5. ELECTRICAL SPECIFICATIONS

#### ABSOLUTE MAXIMUM RATINGS (Ta = 25 °C)

| PARAMETER             | SYMBOL | TEST CONDITIONS                        |                                        |                 | RATING           | UNIT |

|-----------------------|--------|----------------------------------------|----------------------------------------|-----------------|------------------|------|

|                       | Vdd    |                                        |                                        |                 | -0.3 to +7.0     | V    |

| Power supply voltage  | Vpp    |                                        |                                        |                 | -0.3 to +13.5    | V    |

| Input voltage         | VI1    | Except ports 4, 5                      |                                        |                 | -0.3 to VDD +0.3 | V    |

| input voltage         | VI2    | Ports 4, 5                             | Open-o                                 | drain           | -0.3 to +11      | V    |

| Output voltage        | Vo     |                                        |                                        |                 | -0.3 to VDD +0.3 | V    |

| 0.1.1.1.1             | Le.:   | 1 pin                                  |                                        | -15             | mA               |      |

| Output current high   | Іон    | All pins                               |                                        | -30             | mA               |      |

|                       |        | 1 pin                                  |                                        | Peak value      | 30               | mA   |

|                       |        |                                        |                                        | Effective value | 15               | mA   |

| Output current low    |        | Total of norts 0, 2, 2                 |                                        | Peak value      | 100              | mA   |

|                       | lo∟*   |                                        | al of ports 0, 2, 3, 5 Effective value |                 | 60               | mA   |

|                       |        | Total of ports 4 6 7                   | ,                                      | Peak value      | 100              | mA   |

|                       |        | Total of ports 4, 6, 7 Effective value |                                        | Effective value | 60               | mA   |

| Operating temperature | Topt   |                                        |                                        |                 | -40 to +85       | °C   |

| Storage temperature   | Tstg   |                                        |                                        |                 | -65 to +150      | °C   |

\* Calculate the effective value with the formula [Effective value] = [Peak value]  $\times \sqrt{duty}$ .

# CAPACITANCE (Ta = 25 °C, V<sub>DD</sub> = 0 V)

| PARAMETER                    | SYMBOL | TEST CONDITIONS                | MIN. | TYP. | MAX. | UNIT |

|------------------------------|--------|--------------------------------|------|------|------|------|

| Input capacitance            | CIN    |                                |      |      | 15   | pF   |

| Output capacitance           | Соит   | f = 1 MHz                      |      |      | 15   | pF   |

| Input /output<br>capacitance | Сю     | Unmeasured pin returned to 0 V |      |      | 15   | pF   |

| RESONATOR            | RECOMMENDED CIRCUIT | PARAMETER                                   | TEST CONDITIONS                                                               | MIN. | TYP. | MAX.          | UNIT |

|----------------------|---------------------|---------------------------------------------|-------------------------------------------------------------------------------|------|------|---------------|------|

| Ceramic<br>resonator | X1 X2               | Oscillator frequency<br>(fx) *1             |                                                                               | 1.0  |      | 5.0* <b>3</b> | MHz  |

|                      |                     | Oscillation stabilization<br>time <b>*2</b> | After Vod reaches the<br>minimum value in the<br>oscillation voltage<br>range |      |      | 4             | ms   |

|                      |                     | Oscillator frequency<br>(fx) <b>*1</b>      |                                                                               | 1.0  | 4.19 | 5.0* <b>3</b> | MHz  |

| Crystal<br>resonator |                     | Oscillation stabilization time <b>*2</b>    | V <sub>DD</sub> = 4.5 to 6.0 V                                                |      |      | 10            | ms   |

|                      |                     |                                             |                                                                               |      |      | 30            | ms   |

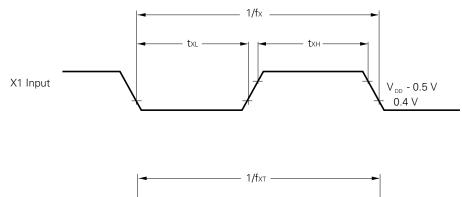

| _                    | X1 X2               | X1 input frequency<br>(fx) *1               |                                                                               | 1.0  |      | 5.0* <b>3</b> | MHz  |

| External<br>clock    | μPD74HCU04          | X1 high and low level widths (txH, txL)     |                                                                               | 100  |      | 500           | ns   |

#### MAIN SYSTEM CLOCK OSCILLATOR CHARACTERISTICS (Ta = -40 to +85 °C, VDD = 2.7 to 6.0 V)

- \* 1. Oscillator characteristics only. Refer to the description of AC characteristics for details of instruction execution time.

- 2. Time required for oscillation to become stabilized after V<sub>DD</sub> reaches MIN. of the oscillation voltage range or after STOP mode release.

- 3. When the oscillator frequency is 4.19 MHz < fx  $\le$  5.0 MHz, do not select PPC = 0011 as instruction execution time. If PCC = 0011 is selected, 1 machine cycle becomes less than 0.95  $\mu$ s, with the result that specified MIN. value 0.95  $\mu$ s can not be observed.

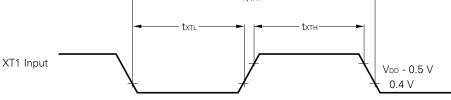

#### SUBSYSTEM CLOCK OSCILLATOR CHARACTERISTICS (Ta = -40 to +85 °C, VDD = 2.7 to 6.0 V)

| RESONATOR            | RECOMMENDED CIRCUIT | PARAMETER                                     | TEST CONDITIONS                | MIN. | TYP.   | MAX. | UNIT |

|----------------------|---------------------|-----------------------------------------------|--------------------------------|------|--------|------|------|

|                      | XT1 XT2             | Oscillator frequency<br>(f <sub>XT</sub> )    |                                | 32   | 32.768 | 35   | kHz  |

| Crystal<br>resonator |                     | Oscillation stabilization                     | V <sub>DD</sub> = 4.5 to 6.0 V |      | 1.0    | 2    | s    |

|                      |                     | time*                                         |                                |      |        | 10   | s    |

| External             | X1 X2               | XT1 input frequency<br>(fxт)                  |                                | 32   |        | 100  | kHz  |

| clock                |                     | XT1 high and low level<br>widths (txth, txtl) |                                | 5    |        | 15   | μs   |

- \* Time required for oscillation to become stabilized after VDD reaches MIN. of the oscillation voltage range or after STOP made release.

- Note When the main system clock and subsystem clock oscillation circuit are used, the area enclosed by dotted line in the figure should be wired as follows to prevent influence from the wiring capacitance, etc..

- Wiring should be as short as possible.

- Do not cross other signal lines.

- Do not place the circuit closed to a line in which varying high current flows.

- The connecting point of oscillation circuit capacitor should always be the same potential as  $V_{DD}$ . Do not connect it to the power supply pattern in which high current flows.

- Do not pick up a signal from the oscillation circuit.

The subsystem clock oscillation circuit is designed to be low amplification circuit for low dissipation current, thus misoperation due to noise occurs more often than with the main system clock oscillation circuit. Therefore, when the subsystem clock is used, care is needed especially for the wiring procedure.

# DC CHARACTERISTICS (Ta = -40 to +85 °C, V<sub>DD</sub> = 2.7 to 6.0 V) (1/2)

| PARAMETER              | SYMBOL | TEST CON                        | DITIONS                                                              | MIN.     | TYP. | MAX.    | UNIT |

|------------------------|--------|---------------------------------|----------------------------------------------------------------------|----------|------|---------|------|

|                        | VIH1   | Ports 2 and 3                   |                                                                      | 0.7 Vdd  |      | Vdd     | V    |

| Input voltage          | VIH2   | Ports 0, 1, 6, 7, RES           | ĒT                                                                   | 0.8 Vdd  |      | Vdd     | V    |

| high                   | Vінз   | Ports 4 and 5                   | Open-drain                                                           | 0.7 Vdd  |      | 10      | V    |

|                        | VIH4   | X1, X2, XT1                     |                                                                      | Vdd -0.5 |      | Vdd     | V    |

|                        | VIL1   | Ports 2, 3, 4 and 5             |                                                                      | 0        |      | 0.3 Vdd | V    |

| Input voltage<br>Iow   | VIL2   | Ports 0, 1, 6, 7, RES           | ET                                                                   | 0        |      | 0.2 VDD | V    |

| -                      | VIL3   | X1, X2, XT1                     |                                                                      | 0        |      | 0.4     | V    |

|                        | Vон1   | Ports<br>0, 2, 3, 6, 7,<br>BIAS | VDD = 4.5 to<br>6.0 V<br>Іон = -1 mA                                 | Vdd -1.0 |      |         | V    |

| Output voltage<br>high |        |                                 | Іон = -100 μА                                                        | Vdd -0.5 |      |         | V    |

|                        | V0H2   | BP0 to BP7<br>(with 2 Іон       | VDD = 4.5 to<br>6.0 V<br>Іон = –100 µА                               | Vdd -2.0 |      |         | V    |

|                        |        | outputs)                        | Іон = -30 μА                                                         | Vdd -1.0 |      |         | V    |

|                        |        | Ports                           | Ports 3, 4 and 5<br>V <sub>DD</sub> = 4.5 to<br>6.0 V<br>IoL = 15 mA |          | 0.4  | 2.0     | v    |

|                        | Vol1   | 0, 2, 3, 4, 5, 6<br>and 7       | V <sub>DD</sub> = 4.5 to<br>6.0 V<br>I <sub>OL</sub> = 1.6 mA        |          |      | 0.4     | V    |

| Output voltage<br>Iow  |        |                                 | Ιοι = 400 μΑ                                                         |          |      | 0.5     | V    |

|                        |        | SB0, 1                          | Open-drain<br>pull-up<br>resistor ≥ 1 kΩ                             |          |      | 0.2 Vdd | V    |

|                        | Vol2   | BP0 to BP7 (with 2              | V <sub>DD</sub> = 4.5 to<br>6.0 V<br>Ιοι = 100 μΑ                    |          |      | 1.0     | V    |

|                        |        | lo∟ outputs)                    | Ιοι = 50 μΑ                                                          |          |      | 1.0     | V    |

|                        | Ілні   | VIN = VDD                       | Other than below                                                     |          |      | 3       | μA   |

| Input leakage          | Ilih2  |                                 | X1, X2, XT1                                                          |          |      | 20      | μA   |

| current high           | Ілнз   | V1N = 10 V                      | Ports 4 and 5<br>(when open-<br>drain)                               |          |      | 20      | μA   |

| Input leakage          | Ilil1  | V <sub>IN</sub> = 0 V           | Other than<br>below                                                  |          |      | -3      | μA   |

| current low            | LIL2   |                                 | X1, X2, XT1                                                          |          |      | -20     | μA   |

# DC CHARACTERISTICS (Ta = -40 to +85 °C, V<sub>DD</sub> = 2.7 to 6.0 V) (1/2)

| PARAMETER                                         | SYMBOL | TEST CONI                                  | DITIONS                                                               |                                  | MIN.                  | TYP. | MAX. | UNIT |

|---------------------------------------------------|--------|--------------------------------------------|-----------------------------------------------------------------------|----------------------------------|-----------------------|------|------|------|

| Output lookage                                    | Iloh1  | Vout = Vdd                                 | Other<br>below                                                        | than                             |                       |      | 3    | μΑ   |

| Output leakage<br>current high                    | Iloh2  | Vout = 10 V                                | Ports 4<br>(when<br>drain)                                            | l and 5<br>open-                 |                       |      | 20   | μΑ   |

| Output leakage<br>current low                     | Ilol   | Vout = 0 V                                 |                                                                       |                                  |                       |      | -3   | μA   |

| On-chip pull-up                                   | RL1    | Ports 0, 1, 2, 3, 6<br>and 7 (Except P00)  | V <sub>DD</sub> = 5<br>±10%                                           | 5.0 V                            | 15                    | 40   | 80   | kΩ   |

| resistor                                          | ne.    | $V_{IN} = 0 V$                             | Vdd = 3.0 V<br>±10%                                                   |                                  | 30                    |      | 300  | kΩ   |

| LCD drive voltage                                 | VLCD   |                                            |                                                                       |                                  | 2.5                   |      | Vdd  | v    |

| LCD output<br>voltage<br>deviation*1<br>(common)  | Vodc   | lo = ±5 μA                                 | VLCD0 =<br>VLCD1 =<br>VLCD ×                                          | =<br>2/3                         | 0                     |      | ±0.2 | V    |

| LCD output<br>voltage<br>deviation*1<br>(segment) | Vodc   | lo = ±5μA                                  | $V_{LCD2} = V_{LCD} \\ \times 1/3 \\ 2.7 V \le V_{LCD} \\ \le V_{DD}$ |                                  | 0                     |      | ±0.2 | v    |

|                                                   |        |                                            | V <sub>DD</sub> = 5<br>±10%*                                          |                                  |                       | 4.5  | 14   | mA   |

|                                                   | Idd1   | 4.19 MHz*3 crystal                         | V <sub>DD</sub> = 3 V<br>±10%*5                                       |                                  |                       | 0.9  | 3    | mA   |

|                                                   |        | - oscillation C1=C2<br>22 pF               | HALT<br>mode                                                          | V <sub>DD</sub> =<br>5 V<br>±10% |                       | 700  | 2100 | μΑ   |

|                                                   |        |                                            |                                                                       | V <sub>DD</sub> =<br>3 V<br>±10% |                       | 300  | 900  | μΑ   |

| Supply current* <b>2</b>                          | Ірдз   | 32 kHz* <b>6</b>                           | Ope-<br>rating<br>mode                                                | V <sub>DD</sub> =<br>3 V<br>±10% |                       | 100  | 300  | μΑ   |

|                                                   | IDD4   | crystal oscillation                        | HALT<br>mode                                                          | V <sub>DD</sub> =<br>3 V<br>±10% |                       | 20   | 60   | μΑ   |

| -                                                 |        |                                            | Vdd =                                                                 | 5 V±10%                          |                       | 0.5  | 20   | μΑ   |

|                                                   | IDD5   | XT1 =<br>0 V STOP mode                     | Vdd =                                                                 |                                  |                       | 0.1  | 10   | μΑ   |

|                                                   |        |                                            | 3 V±10                                                                | %                                | T <sub>a</sub> = 25°C | 0.1  | 5    | μΑ   |

|                                                   | IDD6   | 32 kHz<br>crystal oscillation<br>STOP mode | V <sub>DD</sub> = 3 V ±10%*7                                          |                                  |                       | 5    | 15   | μΑ   |

- \* 1. The voltage deviation is a difference between the segment and common output ideal value (V<sub>LCDn</sub>; n = 0, 1, 2) and output voltage.

- 2. Current flowing in the internal pull-up resistor and LCD split resistor are not included.

- 3. Includes when the subsystem clock is oscillated.

- 4. When the processor clock control register (PCC) is set to 0011 and operated in high-speed mode.

- 5. When the PCC is set to 0000 and operated in low-speed mode.

- 6. When operated by the subsystem clock with the system clock control register (SCC) set to 1011 and the main system clock stops.

- 7. When the STOP instruction is executed during the main system clock operation and the subsystem clock is oscillated.

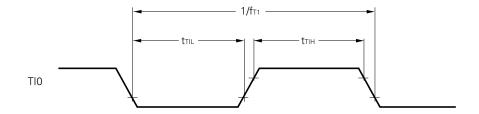

| PARAMETER                                                                               | SYMBOL  | TEST CON                          | DITIONS            | MIN. | TYP. | MAX. | UNIT |

|-----------------------------------------------------------------------------------------|---------|-----------------------------------|--------------------|------|------|------|------|

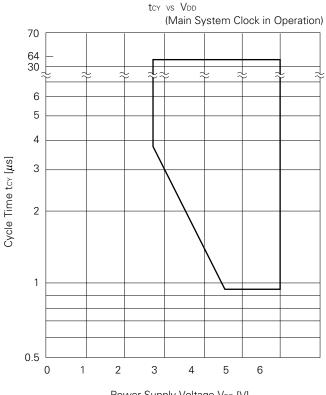

|                                                                                         |         | Operation with main               | VDD = 4.5 to 6.0 V | 0.95 |      | 64   | μs   |

| CPU clock cycle time<br>(minimum instruction<br>execution time = 1<br>machine cycle )*1 | tcy     | system clock                      |                    | 3.8  |      | 64   | μs   |

|                                                                                         | LCY     | Operation with<br>subsystem clock |                    | 114  | 122  | 125  | μs   |

| TIO input fraguanay                                                                     | fтı     | /DD = 4.5 to 6.0 V                |                    | 0    |      | 1    | MHZ  |

| TI0 input frequency                                                                     | 111     |                                   |                    | 0    |      | 275  | kHz  |

| TI0 input high and low-                                                                 | tтıн,   | VDD = 4.5 to 6.0 V                |                    |      |      |      | μs   |

| level widths                                                                            | tτιL    |                                   | 1.8                |      |      | μs   |      |

|                                                                                         |         | INTO                              |                    | *2   |      |      | μs   |

| Interrupt input high and<br>low-level widths                                            | tinth,  | INT1, 2, 4                        |                    | 10   |      |      | μs   |

|                                                                                         | tintl - | KR0–7                             | 10                 |      |      | μs   |      |

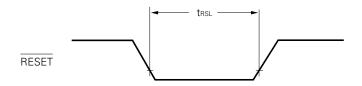

| RESET low-level width                                                                   | trsl    |                                   |                    | 10   |      |      | μs   |

#### AC CHARACTERISTICS (Ta = -40 to +85 $^\circ\text{C}$ , Vdd = 2.7 to 6.0 V)

- CPU clock (Φ) cycle time is determined by oscillator frequency of the connected resonator, system clock control register (SCC) and processor clock control register (PCC). Characteristics for power supply voltage V<sub>DD</sub> vs • cycle time t<sub>CY</sub> in main system clock operation is shown below.

- 2. It becomes 2tcy or 128/fx by interrupt mode register (IM0) setting.

Power Supply Voltage V<sub>DD</sub> [V]

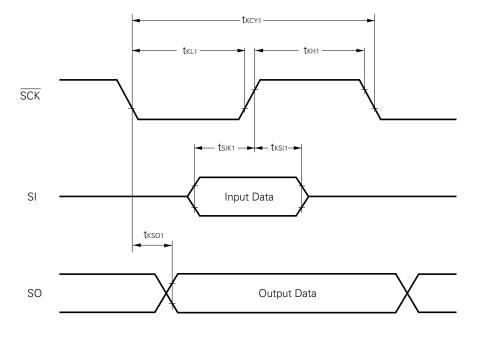

#### **Serial Transfer Operation**

# 2-wire and 3-wire serial I/O mode (SCK...Internal clock output)

| PARAMETER                            | SYMBOL | TEST CON                       | DITIONS                        | MIN. | TYP. | MAX. | UNIT |

|--------------------------------------|--------|--------------------------------|--------------------------------|------|------|------|------|

|                                      |        | V <sub>DD</sub> = 4.5 to 6.0 V | 1600                           |      |      | ns   |      |

| SCK cycle time                       | tkcy1  |                                | 3800                           |      |      | ns   |      |

| SCK high and low level               | tĸ∟1   | V <sub>DD</sub> = 4.5 to 6.0 V | tксү1/2-50                     |      |      | ns   |      |

| widths                               | tкнı   |                                | tксү1/2–150                    |      |      | ns   |      |

| SI setup time (to $\overline{SCK}$ ) | tsik1  |                                |                                | 150  |      |      | ns   |

| SI hold time (from SCK↑)             | tksi1  |                                |                                | 400  |      |      | ns   |

| SO output delay time                 | tuoon  | RL = 1 k Ω, CL = 100 pF*       | V <sub>DD</sub> = 4.5 to 6.0 V |      |      | 250  | ns   |

| from SCK↓                            | tkso1  | ni – 1 k 32, ol – 100 pr       |                                |      |      | 1000 | ns   |

\*  $R_{L}$  and  $C_{L}$  are SO output line load resistance and load capacitance, respectively.

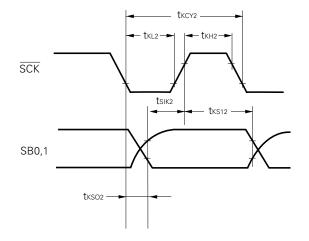

#### 2-wire and 3-wire serial I/O mode (SCK...External clock input)

| PARAMETER                                        | SYMBOL | TEST CON                                               | DITIONS                                  | MIN. | TYP. | MAX. | UNIT |

|--------------------------------------------------|--------|--------------------------------------------------------|------------------------------------------|------|------|------|------|

| SCK cycle time tĸcv2                             |        | V <sub>DD</sub> = 4.5 to 6.0 V                         |                                          | 800  |      |      | ns   |

|                                                  | LKCY2  |                                                        |                                          |      |      |      | ns   |

| SCK high and low level                           | tĸ∟2   | $V_{DD} = 4.5 \text{ to } 6.0 \text{ V}$               | 400                                      |      |      | ns   |      |

| widths                                           | tкн2   |                                                        |                                          | 1600 |      |      | ns   |

| SI setup time (to SCK <sup>↑</sup> )             | tsık2  |                                                        |                                          | 100  |      |      | ns   |

| SI hold time (from $\overline{SCK}^{\uparrow}$ ) | tksi2  |                                                        |                                          | 400  |      |      | ns   |

| SO output delay time                             | tkso2  |                                                        | $V_{DD} = 4.5 \text{ to } 6.0 \text{ V}$ |      |      | 300  | ns   |

| from $\overline{SCK}\downarrow$                  | LKSO2  | $R_{L} = 1 \text{ k } \Omega, C_{L} = 100 \text{ pF*}$ |                                          |      |      | 1000 | ns   |

\*  $R_{L}$  and  $C_{L}$  are SO output line load resistance and load capacitance, respectively.

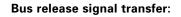

# SBI mode (SCK...Internal clock output (master))

| PARAMETER                                      | SYMBOL       | TEST CON                                         | IDITIONS                       | MIN.       | TYP. | MAX. | UNIT |

|------------------------------------------------|--------------|--------------------------------------------------|--------------------------------|------------|------|------|------|

| SCK cycle time                                 | tксүз        | V <sub>DD</sub> = 4.5 to 6.0 V                   |                                | 1600       |      |      | ns   |

|                                                | LKCY3        |                                                  |                                | 3800       |      |      | ns   |

| SCK high and low level                         | tкьз         | V <sub>DD</sub> = 4.5 to 6.0 V                   |                                | tксүз/2-50 |      |      | ns   |

| widths                                         | tкнз         |                                                  | tксүз/ <b>2–150</b>            |            |      | ns   |      |

| SB0 and SB1 setup time (to $\overline{SCK}$ )  | tsıкз        |                                                  |                                | 150        |      |      | ns   |

| SB0 and SB1 hold time (from $\overline{SCK}$ ) | tksi3        |                                                  | -                              | tксүз/2    |      |      | ns   |

| SB0 and SB1 output                             | tkso3        |                                                  | V <sub>DD</sub> = 4.5 to 6.0 V | 0          |      | 250  | ns   |

| delay time from $\overline{SCK}\downarrow$     | 1803         | R <sub>L</sub> = 1 k Ω, C <sub>L</sub> = 100 pF* |                                | 0          |      | 1000 | ns   |

| SB0, SB1↓ from SCK↑                            | tкsв         |                                                  |                                | tксүз      |      |      | ns   |

| $\overline{SCK}$ from SB0, SB1 $\downarrow$    | tsвк         |                                                  |                                | tксүз      |      |      | ns   |

| SB0 and SB1 low-level widths                   | <b>t</b> sbl |                                                  |                                | tксүз      |      |      | ns   |

| SB0 and SB1 high-level widths                  | tsвн         |                                                  |                                | tксүз      |      |      | ns   |

\*  $R_{L}$  and  $C_{L}$  are SO output line load resistance and load capacitance, respectively.

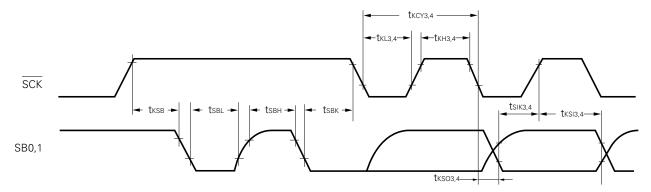

### SBI mode (SCK...External clock input (slave))

| PARAMETER                                                     | SYMBOL        | TEST CON                                              | IDITIONS                                 | MIN.          | TYP. | MAX. | UNIT |

|---------------------------------------------------------------|---------------|-------------------------------------------------------|------------------------------------------|---------------|------|------|------|

| SCK cycle time                                                | tĸcy4         | V <sub>DD</sub> = 4.5 to 6.0 V                        | 800                                      |               |      | ns   |      |

|                                                               | LKCY4         |                                                       |                                          | 3200          |      |      | ns   |

| SCK high and low level                                        | tkl4          | $V_{DD} = 4.5 \text{ to } 6.0 \text{ V}$              |                                          | 400           |      |      | ns   |

| widths                                                        | tкн4          |                                                       | 1600                                     |               |      | ns   |      |

| SB0 and SB1 setup time (to $\overline{\text{SCK}}$ )          | tsik4         |                                                       |                                          | 100           |      |      | ns   |

| SB0 and SB1 hold time (from $\overline{\text{SCK}} \uparrow)$ | tksi4         |                                                       |                                          | tксүз/2       |      |      | ns   |

| SB0 and SB1 output                                            | tkso4         | Rι = 1 k Ω, Cι = 100 pF*                              | $V_{DD} = 4.5 \text{ to } 6.0 \text{ V}$ | 0             |      | 300  | ns   |

| delay time from SCK↓                                          | <b>t</b> K504 | $H_{L} = 1 K \Omega_{2}, C_{L} = 100 \text{ pr}^{-1}$ |                                          | 0             |      | 1000 | ns   |

| SB0, SB1↓ from SCK↑                                           | tкsв          |                                                       | 1                                        | tксү4         |      |      | ns   |

| SCK from SB0, SB1↓                                            | tsвк          |                                                       |                                          | <b>t</b> ксү4 |      |      | ns   |

| SB0 and SB1 low-level widths                                  | <b>t</b> sbl  |                                                       |                                          | tксү4         |      |      | ns   |

| SB0 and SB1 high-level widths                                 | tsвн          |                                                       |                                          | <b>t</b> ксү4 |      |      | ns   |

\*  $R_{L}$  and  $C_{L}$  are SO output line load resistance and load capacitance, respectively.

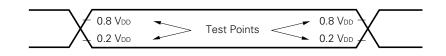

# AC Timing Test Points (Except X1 and XT1 Inputs)

# **Clock Timing**

# TI0 Timing

#### **Serial Transfer Timing**

3-wire serial I/O mode:

# 2-wire serial I/O mode:

#### **Serial Transfer Timing**

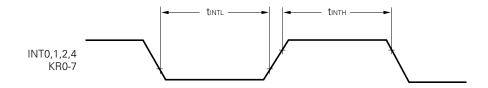

#### Command signal transfer:

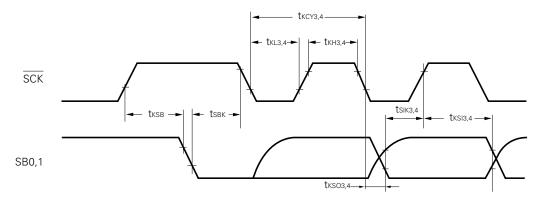

#### Interrupt Input Timing

# **RESET** Input Timing

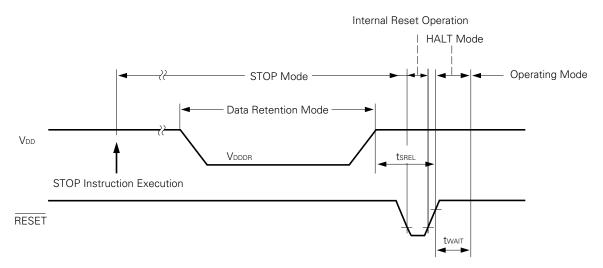

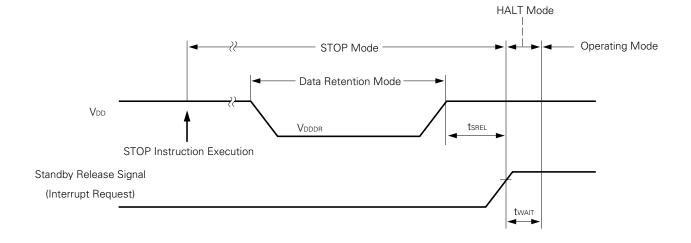

# DATA MEMORY STOP MODE LOW POWER SUPPLY VOLTAGE DATA RETENTION CHARACTERISTICS (Ta = -40 to +85 $^{\circ}$ C)

| PARAMETER                                     | SYMBOL | TEST CONDITIONS              | MIN. | TYP.   | MAX. | UNIT |

|-----------------------------------------------|--------|------------------------------|------|--------|------|------|

| Data retention power supply voltage           | Vdddr  |                              | 2.0  |        | 6.0  | V    |

| Data retention power supply current <b>*1</b> | Idddr  | $V_{DDDR} = 2.0 V$           |      | 0.1    | 10   | μΑ   |

| Release signal set time                       | tsrel  |                              | 0    |        |      | μs   |

| Oscillation stabilization wait                | t      | Release by RESET             |      | 217/fx |      | ms   |

| time * <b>2</b>                               | twait  | Release by interrupt request |      | *3     |      | ms   |

- \* 1. Current to the internal pull-up resistor is not included.

- 2. Oscillation stabilization wait time is time to stop CPU operation to prevent unstable operation upon oscillation start.

- 3. According to the setting of the basic interval timer mode register (BTM) (see below).

| втмз | BTM2 | BTM1 | BTM0 | Wait Time                                 |

|------|------|------|------|-------------------------------------------|

|      |      |      | 2    | (Values at fxx = 4.19 MHz in parentheses) |

| —    | 0    | 0    | 0    | 2 <sup>20</sup> /fxx (approx. 250 ms)     |

| —    | 0    | 1    | 1    | 2 <sup>17</sup> /fxx (approx. 31.3 ms)    |

| _    | 1    | 0    | 1    | 2 <sup>15</sup> /fxx (approx. 7.82 ms)    |

| —    | 1    | 1    | 1    | 2 <sup>13</sup> /fxx (approx. 1.95 ms)    |

# Data Retention Timing (STOP Mode Release by RESET)

#### Data Retention Timing (Standby Release Signal: STOP Mode Release by Interrupt Signal)

#### DC PROGRAMMING CHARACTERISTICS (Ta = -25 to $\pm 5$ °C, V<sub>DD</sub> = 6.0 $\pm 0.25$ V, V<sub>PP</sub> = 12.5 $\pm 0.3$ V, V<sub>ss</sub> = 0 V)

| PARAMETER                | SYMBOL | TEST CONDITIONS      | MIN.                 | TYP. | MAX.    | UNIT |

|--------------------------|--------|----------------------|----------------------|------|---------|------|

| Input voltage high       | VIH1   | Except X1, X2        | 0.7 VDD              |      | Vdd     | V    |

| input voltage nigh       | VIH2   | X1, X2               | V <sub>DD</sub> -0.5 |      | Vdd     | V    |

|                          | VIL1   | Except X1, X2        | 0                    |      | 0.3 Vdd | V    |

| Input voltage low        | VIL2   | X1, X2               | 0                    |      | 0.4     | V    |

| Input leakage current    | lu     | VIN = VIL or VIH     |                      |      | 10      | μA   |

| Output voltage high      | Vон    | Іон = –1mA           | Vdd -1.0             |      |         | V    |

| Output voltage low       | Vol    | lol = 1.6 mA         |                      |      | 0.4     | V    |

| VDD power supply current | loo    |                      |                      |      | 30      | mA   |

| VPP power supply current | Ірр    | MD0 = VIL, MD1 = VIH |                      |      | 30      | mA   |

Note 1. VPP including overshoot should not exceed +13.5 V.

2.  $V_{\text{DD}}$  should be applied before  $V_{\text{PP}}$  and should be cut after  $V_{\text{PP}}.$

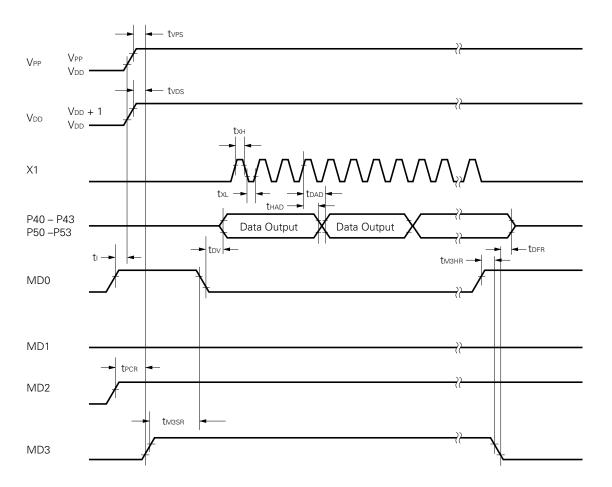

#### AC PROGRAMMING CHARACTERISTICS (Ta = 25 to $\pm 5$ °C, V<sub>DD</sub> = 6.0 $\pm 0.25$ V, V<sub>PP</sub> = 12.5 $\pm 0.3$ V, V<sub>SS</sub> = 0 V)

| PARAMETER                                          | SYMBOL       | *1           | TEST CONDITIONS                                      | MIN.  | TYP. | MAX. | UNIT |

|----------------------------------------------------|--------------|--------------|------------------------------------------------------|-------|------|------|------|

| Address setup time*2 (to MD0 $\downarrow$ )        | tas          | tas          |                                                      | 2     |      |      | μs   |

| MD1 setup time (to MD0 $\downarrow$ )              | tмıs         | toes         |                                                      | 2     |      |      | μs   |

| Data setup time (to MD0 $\downarrow$ )             | tos          | tos          |                                                      | 2     |      |      | μs   |

| Address hold time*2 (from MD0 ↑)                   | tан          | tан          |                                                      | 2     |      |      | μs   |

| Data hold time (to MD0 $\uparrow$ )                | tdн          | tрн          |                                                      | 2     |      |      | μs   |

| Data output float delay time from MD0 $\uparrow$   | <b>t</b> DF  | <b>t</b> df  |                                                      | 0     |      | 130  | ns   |

| VPP setup time (to MD3 $\uparrow$ )                | tvps         | tvps         |                                                      | 2     |      |      | μs   |

| V <sub>DD</sub> setup time (to MD3 ↑)              | tvds         | tvcs         |                                                      | 2     |      |      | μs   |

| Initial program pulse width                        | tpw          | tpw          |                                                      | 0.95  | 1.0  | 1.05 | ms   |

| Additional program pulse width                     | topw         | topw         |                                                      | 0.95  |      | 21.0 | ms   |

| MD1 setup time (to MD1 $\uparrow$ )                | tмos         | tces         |                                                      | 2     |      |      | μs   |

| Data output delay time from MD0 $\downarrow$       | tdv          | tdv          | MD0 = MD1 = VIL                                      |       |      | 1    | μs   |

| MD1 hold time (from MD0 ↑)                         | tм1н         | <b>t</b> oeh | tм1н + tм1к ≥ 50 <i>μ</i> s                          | 2     |      |      | μs   |

| MD1 recovery time (from MD0 $\downarrow$ )         | tm1R         | tor          | $1 \text{ min} + 1 \text{ min} \ge 50 \ \mu\text{s}$ | 2     |      |      | μs   |