ES9018C2M Ultra 32-bit Stereo Mobile Audio DAC Product Brief

The *ES9018C2M SABRE*<sup>32</sup> *Reference DAC* is a high-performance 32-bit, 2-channel audio D/A converter targeted for audiophile-grade portable applications such as mobile phones and digital music players, consumer applications such as Blu-ray players, audio pre-amplifiers and A/V receivers, as well as professional applications such as recording systems, mixer consoles and digital audio workstations.

Using the critically acclaimed ESS patented 32-bit HyperStream<sup>™</sup> DAC architecture and Time Domain Jitter Eliminator, the **ES9018C2M SABRE<sup>32</sup> Reference DAC** delivers a DNR of up to 127dB and THD+N of –120dB, a performance level that will satisfy the most demanding audio enthusiasts.

The *ES9018C2M SABRE*<sup>32</sup> *Reference DAC*'s 32-bit HyperStream<sup>™</sup> architecture can handle up to 32-bit, 384kHz PCM data via I<sup>2</sup>S, DSD-11.2MHz data as well as mono mode for highest performance applications. Both synchronous and ASRC (asynchronous sample rate conversion) modes are supported.

The **ES9018C2M SABRE<sup>32</sup> Reference DAC** is comes in a 25-Ball WLCSP package and consumes less than 40mW in normal operating mode (< 1mW in standby mode)

The **ES9018C2M SABRE<sup>32</sup> Reference DAC** sets a new standard for high quality audio performance, **SABRE SOUND**®, in easy-to-use form factor for today's most demanding digital audio applications.

| FEATURE                                                            |             | DESCRIPTION                                                                                                                                                                                                              |

|--------------------------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Patented 32-bit HyperStream™ DAC<br>○ +127dB DNR<br>○ -120dB THD+N | 0           | Industry's highest performance 32-bit audio DAC Sabre <sup>32</sup> DAC with<br>unprecedented dynamic range and ultra low distortion<br>Supports both synchronous and ASRC (asynchronous sample rate<br>converter) modes |

| Patented Time Domain Jitter Eliminator                             | 0           | Unmatched audio clarity free from input clock jitter                                                                                                                                                                     |

| 64-bit accumulator and 32-bit processing                           | 0           | Distortion free signal processing                                                                                                                                                                                        |

| Integrated DSP Functions                                           | 0<br>0<br>0 | Click-free soft mute and volume control<br>Programmable Zero detect<br>De-emphasis for 32kHz, 44.1kHz, and 48kHz sampling                                                                                                |

| Customizable output configuration                                  | 0           | Mono or stereo output in current or voltage mode based on performance criterion                                                                                                                                          |

| I <sup>2</sup> C control                                           | 0           | Allows software control of DAC features                                                                                                                                                                                  |

| 25-Ball (2.00mm x 2.15mm) WLCSP                                    | 0           | Minimizes PCB footprint                                                                                                                                                                                                  |

| < 40mW operating, < 1mW standby power                              | 0           | Maximizes battery life                                                                                                                                                                                                   |

| Versatile digital input                                            | 0           | Supports SPDIF, PCM (I <sup>2</sup> S, LJ 16-32-bit) or DSD input                                                                                                                                                        |

| Customizable filter characteristics                                | 0<br>0      | User programmable filter allowing custom roll-off response<br>Bypassable oversampling filter                                                                                                                             |

### **APPLICATIONS**

- Mobile phones / Tablets / Digital music players / Portable multimedia players

- Blu-ray / SACD / DVD-Audio player

- Audio preamplifier and A/V receiver

- · Professional audio recording systems / Mixing consoles / Digital audio workstation

### ES9018C2M Product Brief

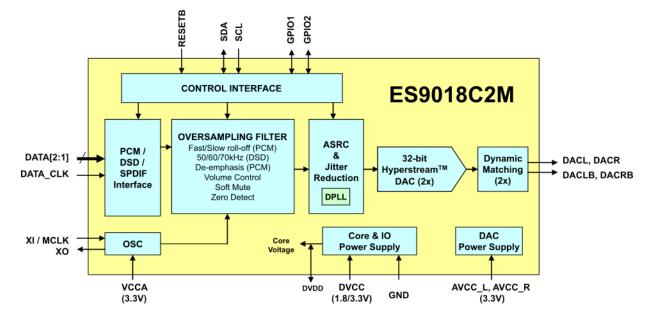

## FUNCTIONAL BLOCK DIAGRAM

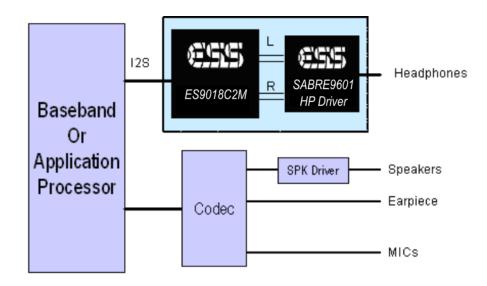

## **TYPICAL APPLICATION DIAGRAM**

## ES9018C2M Datasheet

0.1

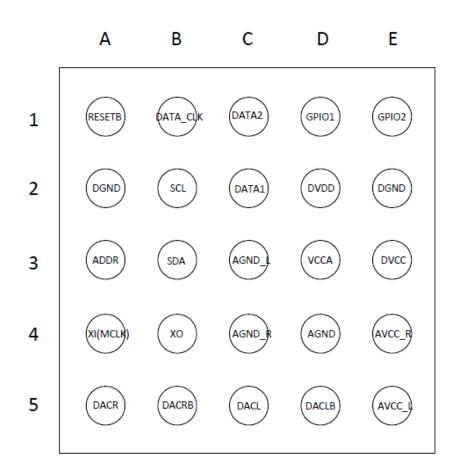

## PIN LAYOUT: BOTTOM VIEW

Bottom View (Bumps facing up)

0.1

### ES9018C2M Product Brief

### **PIN DESCRIPTIONS**

| Pin | Name      | Pin Type | Reset State      | Pin Description                                                                                                                                                                                        |

|-----|-----------|----------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1  | RESETB    | I        | Tri-stated       | Master Reset / Power Down (active low)                                                                                                                                                                 |

| A2  | DGND      | Ground   | Ground           | Digital Ground                                                                                                                                                                                         |

| A3  | ADDR      | I        | Tri-stated       | I <sup>2</sup> C Address Select                                                                                                                                                                        |

| A4  | XI (MCLK) | AI       | Floating         | XTAL / MCLK Input                                                                                                                                                                                      |

| A5  | DACR      | AO       | Driven to ground | Differential Positive Analog Output Right                                                                                                                                                              |

| B1  | DATA_CLK  | I/O      | Tri-stated       | Master mode off: Input for PCM Bit Clock or<br>DSD Bit Clock or SPDIF Input 1.<br>Master mode on: Output for PCM Bit Clock                                                                             |

| B2  | SCL       | I        | Tri-stated       | I <sup>2</sup> C Serial Clock Input                                                                                                                                                                    |

| B3  | SDA       | I/O      | Tri-stated       | I <sup>2</sup> C Serial Data Input/Output                                                                                                                                                              |

| B4  | ХО        | AO       | Floating         | XTAL Out                                                                                                                                                                                               |

| B5  | DACRB     | AO       | Driven to ground | Differential Negative Analog Output Right                                                                                                                                                              |

| C1  | DATA2     | I        | Tri-stated       | DSD Data2 (R) or PCM Data CH1/CH2 or SPDIF Input 2                                                                                                                                                     |

| C2  | DATA1     | I        | Tri-stated       | Master mode off: Input for DSD Data1 (L) or<br>PCM Frame Clock or SPDIF Input 3.<br>Master mode on: Output for PCM Frame Clock                                                                         |

| C3  | AGND_L    | I/O      | Tri-stated       | Analog Ground for Left Channel                                                                                                                                                                         |

| C4  | AGND_R    | Ground   | Ground           | Analog Ground for Right Channel                                                                                                                                                                        |

| C5  | DACL      | AO       | Driven to ground | Differential Positive Analog Output Left                                                                                                                                                               |

| D1  | GPIO1     | I/O      | Tri-stated       | GPIO1                                                                                                                                                                                                  |

| D2  | DVDD      | Power    | Power            | Digital Core Voltage, nominally +1.2V, generated by a regulator from DVCC. DVDD needs to be externally supplied for high XI / MCLK frequency. Please refer to the section about DVDD supply on page 8. |

| D3  | VCCA      | Power    | Power            | Analog +3.3V for OSC                                                                                                                                                                                   |

| D4  | AGND      | Ground   | Ground           | Analog Ground                                                                                                                                                                                          |

| D5  | DACLB     | AO       | Driven to ground | Differential Negative Analog Output Left                                                                                                                                                               |

| E1  | GPIO2     | I/O      | Tri-stated       | GPIO2                                                                                                                                                                                                  |

| E2  | DGND      | Ground   | Ground           | Digital Ground                                                                                                                                                                                         |

| E3  | DVCC      | Power    | Power            | Digital +1.8V to +3.3V                                                                                                                                                                                 |

| E4  | AVCC_R    | Power    | Power            | Analog AVCC for Right Channel                                                                                                                                                                          |

| E5  | AVCC_R    | Power    | Power            | Analog AVCC for Left Channel                                                                                                                                                                           |

0.1

# **ORDERING INFORMATION**

| Part Number | Description                                                     | Package      |

|-------------|-----------------------------------------------------------------|--------------|

| ES9018C2M   | Sabre <sup>32</sup> Reference 32-bit Low Power Stereo Audio DAC | 25-pin WLCSP |

## **Revision History**

| Rev. | Date         | Notes           |

|------|--------------|-----------------|

| 0.1  | Sept 9, 2022 | Initial release |

© 2022 ESS Technology, Inc.

ESS IC's are not intended, authorized, or warranted for use as components in military applications, medical devices or life support systems. ESS assumes no liability whatsoever and disclaims any expressed, implied or statutory warranty for use of ESS IC's in such unsuitable applications.

No part of this publication may be reproduced, stored in a retrieval system, transmitted, or translated in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without the prior written permission of ESS Technology, Inc. ESS Technology, Inc. makes no representations or warranties regarding the content of this document. All specifications are subject to change without prior notice. ESS Technology, Inc. assumes no responsibility for any errors contained herein. U.S. patents pending.