# **DP5 Enhanced Digital Processor Product Migration Guide**

Amptek Inc is introducing a family of enhanced X-ray spectroscopy products, based on a new generation digital pulse processor, the DP5. The DP5 will provide better performance, new signal processing features, improved data processing algorithms, faster data transfers, and a simpler interface. Amptek has also developed an enhanced power supply board for use with Amptek detectors and preamplifiers, the PC5. Products now available using the DP5 and PC5 include:

- 1. The X-123SDD, a significantly enhanced X-123 which uses the new silicon drift detector (SDD), the DP5 digital processor, and a new PC5 power supply module.

- 2. The DP5/PC5 combination, used primarily by OEMs with Amptek's detectors and preamplifiers.

- 3. The DP5 as a standalone unit.

The DP5 implements all of the features and performance of the DP4, with many enhancements. Communication protocols and software are generally compatible with the DP4. Specifically, accessing new features of the DP5 requires software changes but software written for the DP4 will work with the DP5 with minor changes, providing the capabilities of the DP4.

This document describes how users of the existing products can migrate to the new family of products. The focus of this document is on the changes to the products and their interfaces and presume familiarity with the prior products. This document should be used together with the DP4 User Manual.

DP5

DP5/PC5 stack

DP5/PC5 stack back connector view

X-123SDD

Amptek Inc. Page 1 of 39

# 1. FREQUENTLY ASKED QUESTIONS

# 1.1 WHAT ENHANCEMENTS WILL BE FOUND IN THE DP5 VS. THE DP4?

## Performance enhancements

- Faster peaking time available, allowing higher input count rates. Shortest peaking time is 0.2 μsec (equivalent to 80 nsec shaping time).

- Additional peaking times are available, with over 350 settings covering 0.2 μsec to 102 μsec.

- Reduced dead time allowing higher throughput. Dead time is typically 10% shorter.

- Dead time due to USB & RS232 transfers is significantly reduced.

- Improved dead time measurement for more accurate corrections at high rate.

- Fast channel peaking time as short as 0.1 μsec (40 nsec shaping time). This improves pile-up rejection, measurement of incoming count rate, and risetime discrimination.

- Larger gain range, with all ranges overlapping. (16 analog gains, from 1x to 100x.)

- Lower noise analog prefilter. This improves resolution with the lowest noise detectors.

- Input offset, input polarity, and preamp pole zero under software control.

- Software control of the offset channel in the output spectrum, permitting zero offset.

#### Interface enhancements

- Ethernet (10-base T) (will be available summer 09)

- USB upgraded to 2.0 full speed (12 Mbps).

- RS232 upgraded to 115 kbaud (57.6 kbaud selectable).

- No daughter boards (PC4-2, etc) required for DP5 operation.

- o Power supplies are now on the DP5 board, so it only requires +5V input.

- DP5 can be powered from USB (but not when connected to PC5 for Amptek detectors).

- Communication connectors on the DP5 board.

- Power supply board for Amptek's XR100 detectors (new PC5) is under software control, to set temperature and high voltage bias.

- Firmware, both in FPGA and microcontroller, can be upgraded via standard serial interfaces by the user.

- New "List Mode" will be available in the next release. Instead of a spectrum, each event generates an amplitude and a time tag, which are stored and can be downloaded.

- New "Setup" spectrum can be acquired, showing the noise Gaussian, events rejected by pile-up rejection and risetime discrimination, by gating logic, etc. Useful for optimizing parameters.

- A "board interconnect" has been added to simply interface to daughter boards with other capabilities, or to systems containing multiple digital processors.

- A 512kB low-power SRAM was added to the DP5, adding buffering flexibility. For example, sequential spectra can be buffered for later transmission to the PC.

Amptek Inc. Page 2 of 39

# 1.2 IS THE DP5 BACKWARD COMPATIBLE WITH THE DP4?

As close as feasible but some changes are inevitable.

## Software

- A new release of Amptek's ADMCA software incorporates the DP5 interface over USB. With ADMCA

one can access all of the DP5's features in the same manner as the DP4 or PX4.

- The DP5 uses FLASH memory to store its power-up configuration and some parameters which are unsupported by the legacy DP4 & PX4 protocols (for example, switching to 80MHz operation to access the fastest peaking times, selecting 115k/57.6k RS232 operation, etc.). These options can be selected via the standard serial interfaces.

- For users who have written or are writing their own software, there are a few options.

- o To use the new functions and features of the DP5, new data packets and communications libraries are required. This implies some software changes, for either USB or RS232.

- With RS232, the DP5 recognizes the same data packets used with the DP4 and PX4. There are some parameters which must be specified with the DP5 which were not used in the DP4, e.g. input offset. These can be set once, during initial product configuration, and are then stored in the DP5's EEPROM. A stand-alone application is provided by Amptek to set the new features and store them. With this legacy DP4 software can be used unchanged.

- With USB, the DP5 recognizes the same packets for commanding and for readout of spectra and status packets. Readout of configuration and of oscilloscope packets requires minor software changes. (The DP5 microcontroller supports fewer USB 'endpoints' or 'pipes' than the DP4 microcontroller, so a few required remapping.) An updated Windows API interface (DPP API) is available that is also backwards compatible with the DP4 and PX4.

# Physical

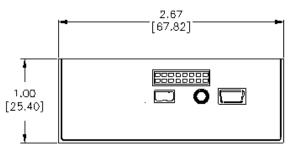

## DP5 Standalone

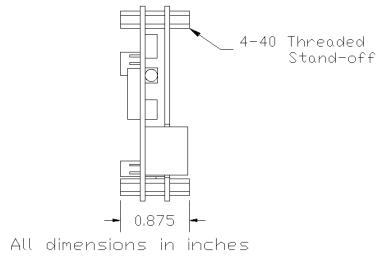

- The DP5 has the same physical size and mounting holes as the DP4.

- The preamp input connector and DAC output connector are different, but in the same location.

- Additional interface connectors have been added, eliminating the need for daughter boards and reducing the number of supply voltages required. The backplane (JP6) and auxiliary (JP9) connectors have been changed and moved. Standard USB, serial, Ethernet, and power supply connectors are now on the DP5.

# X-123SDD and DP5/PC5

- The X-123SDD USB and serial connectors have been moved slightly. A different power connector is now used. An Ethernet connector has been added, although it is not yet supported in software.

- With the PC5, the 8 pin power & serial header used previously is still available. The same USB and serial connectors are still available, moved from the PC4-2 and PC4-3 to the DP5.

- The power dissipation will increase to 0.9 W for a 20 MHz clock. To use faster peaking times, an 80 MHz clock is required, with dissipation of 1 W typical.

## 1.3 How were these enhancements achieved?

- The DP4's ADC and digital processor operated at a 20 MHz clock rate. The DP5 can be clocked at 20 or 80 MHz. The higher clock rates permit the faster peaking times in both the main and fast channels but the unit dissipates more power in this mode. For systems not requiring the fastest peaking times or operating at the higher rates, the 20 MHz clock can be used to reduce power.

- A number of improvements were made to the digital signal processing algorithms and to the analog

prefilter. Amptek has conducted significant in-house research and development on digital signal

processors since the release of initial DP4 and has tailored the design to meet the unique needs of

many customers. These developments were folded into the new DP5.

Amptek Inc. Page 3 of 39

• The constantly shrinking physical sizes of many components permitted us to move the power supplies and connectors from daughter boards, used with the DP4, onto the DP5. This significantly simplifies system integration.

# **CONTENTS**

| 1.   | Frequently Asked Questions                              | 2  |

|------|---------------------------------------------------------|----|

| 1.1  | What enhancements will be found in the DP5 vs. the DP4? | 2  |

| 1.2  | ls the DP5 backward compatible with the DP4?            | 3  |

| 1.3  | How were these enhancements achieved?                   | 3  |

| 2.   | Changes to ADMCA                                        | 5  |

| 3.   | Changes to Signal Processing Algorithms                 | 8  |

| 3.1  | DP5 Major Function Blocks                               | 8  |

| 3.2  | 2 Clock Rate Changes                                    | 9  |

| 3.3  | B Dead Time and Pile-Up Rejection                       | 9  |

| 4.   | Hardware Migration                                      | 10 |

| 4.1  | X-123SDD                                                | 10 |

| 4.2  | 2 DP5 Alone                                             | 11 |

| 4.3  | B DP5 with PC5                                          | 17 |

| 5.   | Software Migration                                      | 18 |

| 5.1  | Overview                                                | 18 |

| 5.2  | Changes to Configuration Packets                        | 21 |

| 5.3  | B Data Packet Changes                                   | 28 |

| 5.4  | Changes to RS232 Interface                              | 32 |

| 5.5  | Changes to USB Interface                                | 32 |

| 5.6  | USB Vendor Requests                                     | 33 |

| 5.7  | Hints for Software Migration                            | 34 |

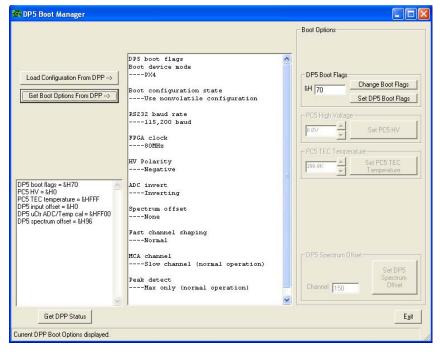

| 5.8  | B Using the Boot Manager                                | 35 |

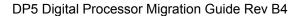

| 5.9  | Uploading Firmware and Software                         | 37 |

| 5.10 | 0 Versions                                              | 39 |

# 2. CHANGES TO ADMCA

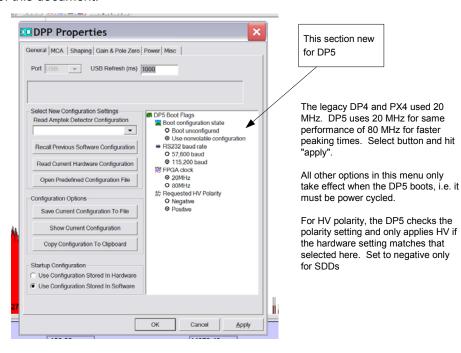

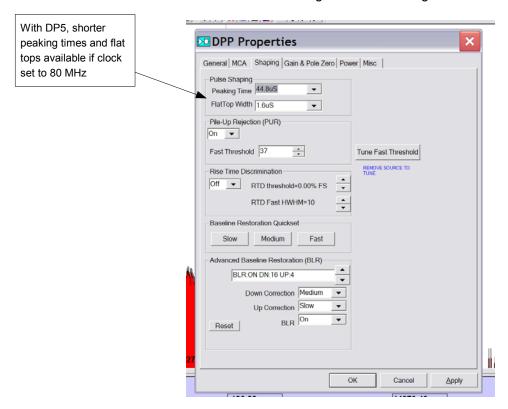

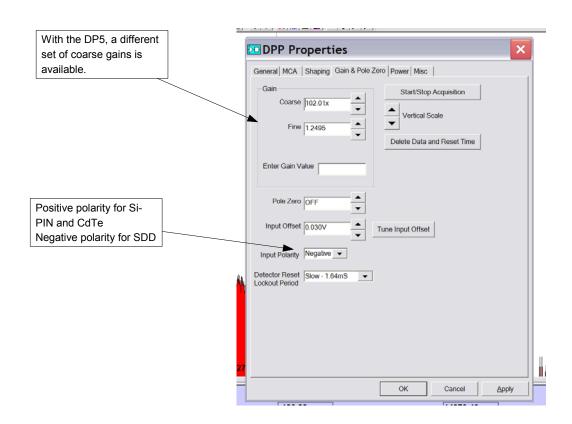

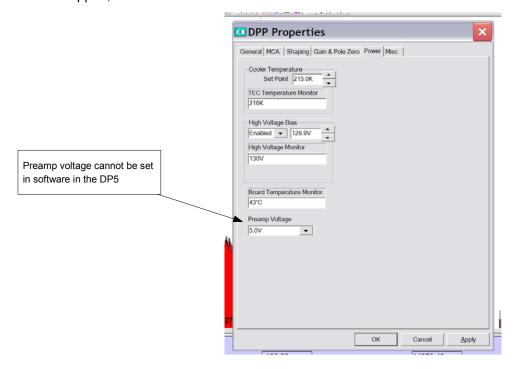

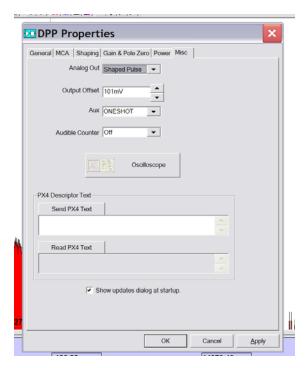

Many users rely on Amptek's ADMCA software for interfacing to the DP4 and PX4. With ADMCA, migration to the DP5 is quite straightforward. There are some additional configuration options in the "Acquisition Setup" button (DPP Properties). The screen captures below show which portions of the "acquisition setup" menus have changed. Note: the latest version of ADMCA, version 1.0.8.17, supports the DP5. For more information on changes to the software interface and an explanation of what is happening "under the hood" in the DP5, refer to section 5 of this document.

Amptek Inc. Page 5 of 39

Amptek Inc. Page 6 of 39

When you change the ADC clock, hit apply and then "OK". You will then need to reset shaping time, BLR settings, and detector reset lockout period. Note that the updated values only appear if the software is acquiring data; if acquisition has stopped, "stale" values are shown.

Note that the X-123SDD supports software control of power supplies, unlike the previous X123.

Amptek Inc. Page 7 of 39

## 3. CHANGES TO SIGNAL PROCESSING ALGORITHMS

This section documents changes made to the signal processing algorithms used in the legacy instruments, the DP4 and PX4.

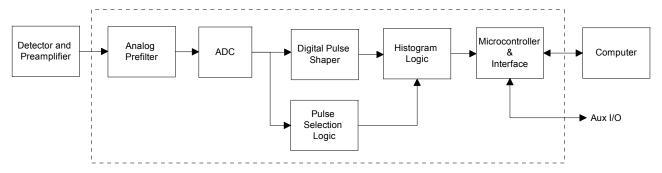

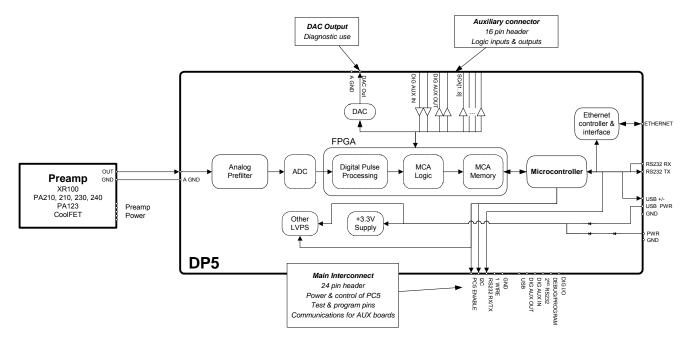

## 3.1 DP5 Major Function Blocks

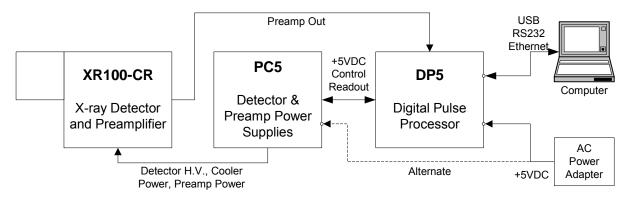

Figure 1 shows how the DP5 is used in the complete signal processing chain of a nuclear instrumentation system and its main function blocks. This is unchanged from the DP4. Like the DP4 and PX4, the input to the DP5 is the preamplifier output. The DP5 digitizes the preamplifier output, applies real-time digital processing to the signal, detects the peak amplitude (digitally), and bins this value in its histogram Ming memory, generating an energy spectrum. The spectrum is then transmitted over the DP5's serial interface to the user's computer. The DP5 has the same main function blocks, implementing the same basic functionality, although some of the details have been changed to improve performance.

Figure 1. Block diagram of the DP5 in a complete system.

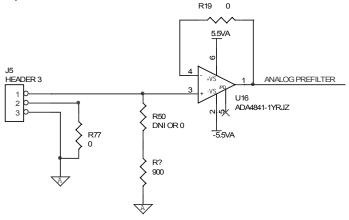

**Analog Prefilter:** The input to the DP5 is the output of a charge sensitive preamplifier. The analog prefilter circuit prepares this signal for accurate digitization. The main functions of this circuit are (1) applying appropriate gain, offset, and inversion (if necessary) to utilize the dynamic range of the ADC, and (2) carrying out some filtering and pulse shaping functions to optimize the digitization.

Changes to the DP5 analog prefilter include (1) adding additional coarse gain settings to provide a larger dynamic range and to provide overlapping gain ranges; (2) replacing the input offset potentiometer with a DAC for software control; (3) making the input polarity under software control; and (4) lower noise circuitry.

**ADC:** The ADC digitizes the output of the analog prefilter at a 20 MHz rate. This stream of digitized values is sent, in real time, into the digital pulse shaper.

The ADC can now be clocked at either 20 MHz or at 80 MHz. The higher frequency permits faster shaping times for better performance at high count rates. Like the DP4/PX4, a 12 bit ADC is used.

**Digital Pulse Shaper:** The ADC output is processed continuously using a pipeline architecture to generate a real time shaped pulse. This carries out pulse shaping as in any other shaping amplifier. The shaped pulse is a purely digital entity. Its output can be routed to a DAC, for diagnostic purposes, but this is not necessary. The peak value of the digital shaped pulse is determined by a peak detect circuit in the pulse shaper. The peak value for each pulse, a single digital quantity, is the primary output of the pulse shaper.

The basic slow pulse shaping is unchanged from the DP4. It is still a trapezoid, but with faster shaping times available. Some of the additional logic has been changed, including (1) improved fast channel shaping for better separation of pulses; (2) minor changes to baseline restoration logic for improved stability; (3) minor changes to peak detect logic for reduced dead time.

**Pulse Selection Logic:** The pulse selection logic rejects pulses for which an accurate measurement cannot be made. It includes pile-up rejection and risetime discrimination.

Pile-up rejection in the DP5 has been changed and results in better performance, i.e. fewer piled-up pulses in the output spectrum. But there are some subtle changes to the piled-up spectrum. The dead time is now measured directly rather than being estimated from the incoming count rate (ICR). Risetime discrimination is unchanged (note: it is not yet functional in the current firmware release). The DP5 will permit the user to measure the spectrum of these piled-up events, which is very useful in optimizing.

Amptek Inc. Page 8 of 39

**Histogram Memory:** The histogram memory operates as in a traditional MCA. When a pulse occurs with a particular peak value, a counter in a corresponding memory location is incremented. The result is a histogram, an array containing, in each cell, the number of events with the corresponding peak value. This is the energy spectrum and is the primary output of the DP5. Auxiliary outputs include eight different single channel analyzers, and both a DAC output and a digital output showing pulse shapes from several points in the signal processing chain.

The basic operation is unchanged. The logic has been streamlined considerably, providing for much faster readout of the spectra, reducing dead time between acquisitions. The DP5 will include a spectrum offset parameter which can be set so that channel zero represents zero energy. The DP5 will be capable of storing and displaying additional spectra, not used during "primary" data acquisition but useful for setup and analysis, such as the spectrum of events rejected by PUR or RTD logic. The DP5 will also include a "List" mode, which stores both the amplitude and arrival time of each event.

**Interface:** The DP5 includes hardware and software to interface between these various functions and the user's computer. A primary function of the interface is to transmit the spectrum to the user. The interface also controls data acquisition, by starting and stopping the processing and by clearing the histogram memory. It also controls certain aspects of the analog and digital shaping, for example setting the analog gain or the pulse shaping time.

The interface hardware and software are as compatible as feasible but have changed somewhat. These changes are documented in sections 4 and 5 of this document.

## 3.2 CLOCK RATE CHANGES

Several time-related settings of the digital processing are implemented in terms of the clock cycles. When the DP5 is set to 20 MHz, these operate as in the DP4. When the ADC clock is set to 80 MHz, there are some changes. First and foremost, the peaking time is defined in terms of clock cycles. If the software uses the same configuration byte for the peaking time, then the actual peaking time is a factor of four faster. The ADMCA software shows the true peaking time. Under the most common operating conditions, the electronic noise increases as short shaping times, so increasing the clock rate often increases noise. The optimum slow threshold setting usually increases with this, so the user must set this properly.

At 20 MHz, the fast channel has a 400 nsec peaking time, as in the DP4. At 80 MHz, the fast channel has a 100 nsec peaking time, equivalent to a semi-Gaussian shaper with 40 nsec time constant. This provides excellent pile-up rejection but the noise in the fast channel generally increases (due to the wider noise bandwidth) and the optimum fast channel threshold will increase as well.

The detector reset lockout interval scales with clock rate, as do the BLR settings. After the ADC clock is changed, if the user wants to keep the same interval, then the reset lockout and BLR settings should be changed appropriately.

## 3.3 DEAD TIME AND PILE-UP REJECTION

Most traditional analog nuclear instrumentation systems have several sources of dead time, including a time due to the duration of the shaped pulse (which is important for counting) and another due "conversion", the time the peak height is sampled and digitized. Most traditional MCAs have a "live time clock" which is turned off during "conversion". So this clock permits one to correct count rates for those lost during conversion. Since the "conversion" time is usually much longer than the pulse shaping time, this is the dominant correction.

Digital processors do not "lose" pulses due to conversion. Since they sample continuously, at the ADC clock speed, there is no conversion time and so no losses. However, the shaped pulses do have a finite duration and therefore some pulses are lost, i.e. not counted, due to overlap of the shaped pulses. This is the "dead time" for which one corrects in a digital processor. This "dead time per pulse" in the DP5 is different from that in the DP4 and the total dead time is measured differently. This difference has no impact on users operating at low count rates but is quite important for those operating at high count rates. In the DP4 (and PX4), there was a fixed dead time per pulse, arising from the peak detect logic, equal to

$$\left(\frac{19}{16}\right)\tau_P + \tau_F$$

[DP4]

Amptek Inc. Page 9 of 39

where  $\tau_P$  is the peaking time and  $\tau_F$  is the flat top duration. To obtain the true incoming count rate, one used the measurement of the incoming count rate (ICR) in the fast channel and corrected for the known dead time of the fast channel.

In the DP5, an improved peak detect algorithm is used. One consequence is that the time required to determine if a pulse occurred (and thus the dead time) depends on the amplitude of the pulse relative to noise. For pulses much larger than noise, the dead time is essentially the peaking time. Dead time is reduced and so fewer counts are lost. However, the dead time increases for pulses near the slow threshold. The DP5's pile-up reject logic uses this same "per pulse dead time". For the vast majority of pulses, well over the noise threshold, it provides a higher throughput while still rejecting pile-up. For pulses very near the noise threshold, however, the fraction of pulses which are accepted will be reduced. To aid in understanding the pile-up behavior, the DP5 will permit the user to acquire and display the spectrum of pulses rejected by PUR and the dead time will be directly measured (these are not yet implemented in ver. 5.00).

The DP5, like the DP4 and PX4, disables data acquisition during the time a spectrum is read out over the serial interface. The "acquisition time" represents the actual time during which data are acquired and will be shorted than the elapsed "real" time. This is discussed in the DP4 documentation. Its operation is unchanged in the DP5, although the dead time is reduced due to faster data transfer logic.

## 4. HARDWARE MIGRATION

This section will discuss hardware changes, such as form factor, connectors, and power dissipation. Software interface changes are discussed in the next section.

## 4.1 X-123SDD

The X-123SDD has much better performance than the X-123 with a Si-PIN, but the interface is virtually unchanged.

- A silicon drift detector (SDD) is used as the detector rather than a Si-PIN. This has better resolution and operates at higher count rates. Information on the SDD can be found at Amptek's website at http://www.amptek.com. From an interface perspective, the optimum configuration for the SDD is different than the Si-PIN but the response and its use is otherwise unchanged.

- As discussed in more detail in the software interface section, the bias voltage and temperature set point in the X-123 were set at the factory by resistors or trim pots. In the X-123SDD these are under software control, providing additional flexibility in configuring the unit.

- The physical dimensions, mass, and mounting points of the X-123 package are unchanged.

- The USB and serial connectors are the same, with locations moved slightly, as shown below.

- A different power connector is used, still supplying +5 VDC. The new connector provides a positive mechanical connection.

- An Ethernet connector will be available in the next product release (summer '09).

- An "auxiliary" connector has been added. This brings out several digital I/O signals, including a timing output, gate input, SCA outputs, and other diagnostics.

- Power dissipation has increased from about 1 watt to approximately 1.5 watts.

Amptek Inc. Page 10 of 39

# 4.1.1 Block Diagram

Figure 2. X-123SDD Block Diagram.

# 4.1.2 Connectors

Figure 3. Mechanical drawing showing connector locations on the X-123SDD. All other mechanical dimensions are unchanged from the standard X-123.

Power

Hirose MQ172-3PA(55).

Auxiliary

2x8 16-pin 2 mm spacing (Samtec part number ASP-135096-01)

Ethernet

Standard Ethernet connector (available summer '09)

USB

Standard USB mini jack

RS-232

Standard 2.5 mm stereo audio jack.

# 4.2 DP5 ALONE

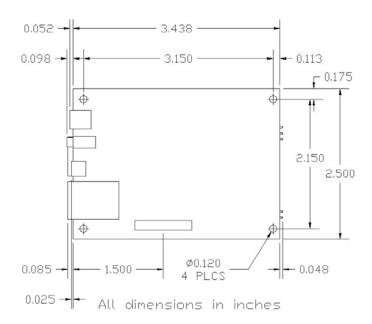

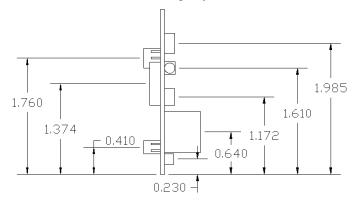

- The overall envelope and locations of the mounting points on the DP5 are unchanged, but the board length has been reduced slightly.

- Power

- The DP5 includes low voltage power supplies. It is powered from a loosely regulated +5 VDC source and generates all of the necessary low voltages. This is different from the DP4, which requires several regulated low voltages.

- o Power dissipation has increased from 600 mW (typical) to 1 W (typical)

- Communications

Amptek Inc. Page 11 of 39

- The serial (RS232) interface now operates at 115k, but 57.6k can still be selected via a 'boot flag'. (See section 5.2.1.)

- o It supports USB 2.0 (full speed, with the same data transfer rates as on the DP4)

- It has support for Ethernet (summer '09)

#### Connectors

- The signal input connector (which connects to a preamp) and the output DAC connector are in the same locations but have changed. The input connector is now a 1x3 right angle header Molex part number 22-28-8032. The DAC output connector is a 1x2 right angle header Molex part number 22-28-8022.

- o The standard configuration for the input circuit is no longer differential and has a +/-4.5V range.

- Communications interface and power connectors are now located on the DP5 board.

Previously, a header on the DP4 took these lines, via a ribbon cable, to a daughter board. The daughter board is no longer required.

- The "main interconnect" between the DP5 and any additional boards, such as the PC5, is completely different. It is a new connector, with new signals, and a new pinout.

- The "auxiliary connector," which brings auxiliary digital inputs/outputs, has been moved.

## Other

A new microcontroller is now used, the Silicon Labs 8051F340. The embedded software has been completely rewritten, now in C instead of assembler.

# 4.2.1 Block Diagram

Amptek Inc. Page 12 of 39

# 4.2.2 DP5 Board Layout

Figure 4. DP5 bottom side, showing key interconnects.

All dimensions in inches

Figure 5. DP5 back/side view.

Amptek Inc. Page 13 of 39

# 4.2.3 J5 Main Interconnect

This connector replaces the JP6 ribbon cable interconnect on the DP4. The primary purpose of J5 is to connect the DP5 to the PC5, Amptek's power supply board for Amptek preamplifiers and detectors. It provides input power in either direction, from DP5 to PC5 or vice-versa and permits the DP5 to control PC5 supplies. Its secondary purpose is to permit addition of planned auxiliary boards such as Bluetooth, WiFi, or X-ray tube controllers. These can connect to the DP5 or to the DP5/PC5 stack. The connector is a 2X12 Socket Strip Samtec part number SMM-112-02-S-D-LC.

| Pin# | Name      | Use            | Pin# | Name                 | Use            |

|------|-----------|----------------|------|----------------------|----------------|

| 1    | GND       |                | 13   | RS232-RX             | PC5, AUX, Test |

| 2    | GND       |                | 14   | RS232-TX             | PC5, AUX, Test |

| 3    | PWR EXT   | PC5, AUX, Test | 15   | RX1/IO               | AUX only       |

| 4    | PWR EXT   | PC5, AUX, Test | 16   | TX1/IO               | AUX only       |

| 5    | C2D       | Test           | 17   | IO0                  | AUX only       |

| 6    | /RST/C2CK | Test           | 18   | IO1                  | AUX only       |

| 7    | AUX IN 1  | AUX only       | 19   | I <sup>2</sup> C SCL | PC5, AUX, Test |

| 8    | AUX OUT 1 | AUX only       | 20   | I <sup>2</sup> C SDA | PC5, AUX, Test |

| 9    | PS ENABLE | PC5 only       | 21   | USB+                 | AUX only       |

| 10   | 1-WIRE    | PC5 only       | 22   | USB-                 | AUX only       |

| 11   | AN_IN     | AUX only       | 23   | GND                  |                |

| 12   | SPARE     |                | 24   | GND                  |                |

- PWR EXT: This is the power connection between the DP5 and the PC5, the input to the regulators on both boards. It can serve as an input to the DP5 (if the external supply is connected to the PC5) or as an output from the DP5 (if the supply is connected to the DP5). It is nominally +5V (4-6V)

- C2D and /RST/C2CK: C2D and C2CK are used when initially programming the μC. Additionally, pulling pin 6 low will hold the entire DP5 in reset. Floating it or pulling it high allows normal operation. These pins are usually only used during manufacturing test.

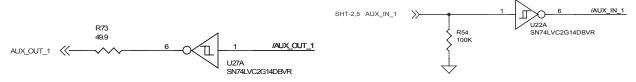

- AUX IN 1 and AUX OUT 1: These are auxiliary digital logic input and output lines from the FPGA. They can be software configured to any one of several functions (ICR, RESET, GATE, etc). They are driven from (into) Schottky buffers (3.3 V logic) with 49.9 $\Omega$  series on AUX OUT (100 k $\Omega$  to GND on AUX IN). These are not used in the PC5, only with AUX boards. These signals also appear on J6.

- PS ENABLE: Open-drain output used by the DP5 to enable the PC5 power supplies. This is only used with the PC5. It is pulled low to turn OFF the PC5 supplies, and floated to turn ON the PC5 supplies. (The PC5 has a 10k pullup to 3.3V on this signal.)

- 1-WIRE: Dallas 1-wire interface, used to communicate with 1-wire PROM in the detector hybrids. This is only used with the PC5.

- RS232-RX, RS232-TX: These are RS232 signals for interfacing the DP4 to a host system. The signal

names are relative to the DP5, i.e. the DP5 receives on the RX pin and transmits on the TX pin. This may

be used with the PC5 and with other units.

- RX1/IO and TX1/IO: These two pins can be assigned (via software) to one of two functions. This requires custom embedded software in the DP5  $\mu$ C. They are not used in the PC5.

- $\circ$  RX1/TX1: This is a second serial interface, which can be used by the  $\mu C$  to communicate with auxiliary devices.

- IO: These become general purpose IO pins from the μC to interface with external hardware.

Amptek Inc. Page 14 of 39

- IO0, IO1: These two pins connect to a I2C port expander and then to the μC. They can be used to communicate with or control external hardware. They can be controlled via serial commands. They are not used in the PC5.

- AN\_IN: This is an uncommitted analog input. The DP5 microcontroller ADC periodically converts this signal, and the result appears in the Status Packet. The input range is 0 - 2.4V. This signal has a high input impedance.

- SDA, SCL: These are the I<sup>2</sup>C bus signals. The DP5 μC is the bus master, though it is possible to communicate with another master, or other slave peripherals. They are used in the PC5 and may be used with Aux.

- USB+, USB-: This is the USB (Universal Serial Bus) communication bus. The DP5 microcontroller contains a USB communication core. They are not used in the PC5.

## Pinout

|            |    | J5<br>CON24A |     |            |               |       |

|------------|----|--------------|-----|------------|---------------|-------|

| GND        | 1  | OONZ-7A      | ] 2 | GND        |               |       |

| PWR_EXT    | 3  |              | 4   | PWR_EXT    |               |       |

| C2D        | 5  |              | 6   | /RST/C2CK  |               |       |

| AUX_IN_1   | 7  | 1            | 8   | AUX_OUT_1  |               |       |

| PS_ENABLE  | 9  | 1            | 10  | 1-WIRE     |               |       |

| AN_IN      | 11 | 1            | 12  | -          | $\circ$       | RPAD2 |

| RS232-RX   | 13 | l '          | 14  | RS232-TX   | $\overline{}$ | J5-12 |

| RX1/RTS/IO | 15 | l '          | 16  | TX1/CTS/IO |               |       |

| 12C_IO0    | 17 | l '          | 18  | I2C_IO1    |               |       |

| SCL        | 19 | l '          | 20  | SDA        |               |       |

| USB+       | 21 |              | 22  | USB-       |               |       |

| GND        | 23 |              | 24  | GND        |               |       |

|            |    |              |     | _          |               |       |

# Physical

- Mates with PCB mount connector (Samtec P/N) TMM-112-01-S-D-SM or with cable (Samtec P/N) TCMD-12-...

- This is a 24 pin connector, with 2 mm spacing.

# 4.2.4 J6 Auxiliary Connector

The primary purpose of this connector is to bring out logic signals which are not required for the primary use of the DP5: acquiring spectra and transmitting then over the serial interface. These are generally "low level" logic signal associated with each pulse processed by the DP5. They are primarily used for synchronizing the DP5 data acquisition to external hardware and for direct counter/timer outputs from the DP5. The signals are described below. The connector is a 2x8 right angle Samtec part number ASP-135096-01.

| Pin # | Name | Pin# | Name      |

|-------|------|------|-----------|

| 1     | SCA1 | 9    | AUX_IN_1  |

| 2     | SCA2 | 10   | AUX_OUT_1 |

| 3     | SCA3 | 11   | AUX_IN_2  |

| 4     | SCA4 | 12   | AUX_OUT_2 |

| 5     | SCA5 | 13   | IO2       |

| 6     | SCA6 | 14   | IO3       |

| 7     | SCA7 | 15   | GND       |

| 8     | SCA8 | 16   | GND       |

## **Physical**

Mates with connector (Samtec P/N) TCSD-08-S(D)-xx.xx-01-F-N.

Amptek Inc. Page 15 of 39

Single Channel Analyzers (SCAs)

- Each of the eight SCAs has an independently assignable LLD and a ULD. If the shaped pulse peaks with the range of an SCA, between its LLD and ULD, then a logic signal is output.

- These outputs produce pulses 100ns wide. Logic low is <0.1V @100  $\mu$ A. Logic high is >3.1V @100

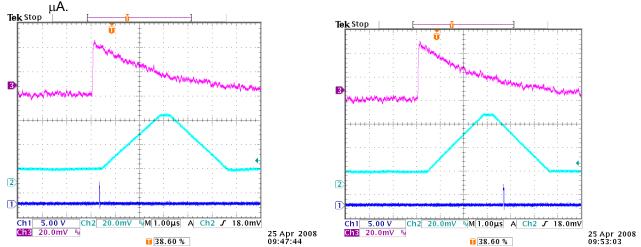

Figure 6. Oscilloscope trace showing the timing of several outputs. In both plots, the pink trace is the input to the ADC. The light blue trace is the shaped output, with a 2.4  $\mu$ sec peaking time and a 0.4  $\mu$ sec flat top. In the left-hand plot, the dark blue trace shows the ICR signal on an AUX\_OUT. In the right-hand plot, the dark blue trace shows an SCA signal.

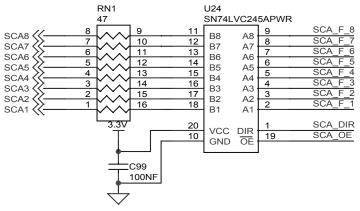

Figure 7. Schematic showing SCA interface hardware.

# AUX\_OUT\_1 and \_2

- Each of these two lines can be configured, via software, to output any one of several logic signals in the FPGA. These logic signals are associated with pulses processed by the FPGA.

- The pulse timing and duration depends on which output is commanded.

- AUX\_OUT\_1 is connected to the Interconnect (J5), to the auxiliary connector (J6), and can be jumpered to the stereo jack (J10). AUX\_OUT\_2 is only connected to the auxiliary connector (J6).

- Logic low is <0.1V. Logic high is >3.1V.

Amptek Inc. Page 16 of 39

- Each of these two lines can be configured, via software, to input any one of several logic signals in the FPGA. These logic signals are associated with pulses processed by the FPGA.

- AUX\_IN\_1 is connected to the Interconnect (J5), to the auxiliary connector (J6), and can be jumpered to the stereo jack (J10). AUX\_IN\_2 is only connected to the auxiliary connector (J6).

# 4.2.5 Configuration Notes

The DP5 has several configuration options, which the user should select or can change.

# Input Range

In the default configuration, the input range of the DP5 is +/-4.5V. This is suitable for most charge amps with resistive or transistor feedback or reset preamps operating from +/- 5V. For reset preamps operating from a larger range, including Amptek's XR100 detectors, a zero ohm resistor should be installed in R50.

Figure 8. Schematic of DP5 analog input.

# Differential Input

The DP5's standard input configuration, shown in Figure 8, is not differential. This is different from the DP4 for which the differential input was standard. The DP5 can be configured in a differential mode. This increases immunity to conducted interference, such as ground loops, but also increases the electronic noise contribution of the DP5's analog circuitry.

## Resistive Feedback Preamps

The DP5's standard input configuration is for a reset preamplifier, with no pole zero resistor. The pole zero circuit changes are essentially the same as for the DP4, as discussed in its user manual, but the reference designators are different. The differentiating capacitor is C69, 6800 pF. The pole zero pot is R102, with nothing installed for the standard configuration.

- 1. Install in R102 a pot such that (R102)(C69) can be adjusted to give the preamp's time constant.

- 2. Remove R26.

- 3. Install a pot in R103. This pot will be in series with 411 ohms. The value of this pot should be such that the parallel combination of R102 and (R103 + 411 ohms) equals 460 ohms.

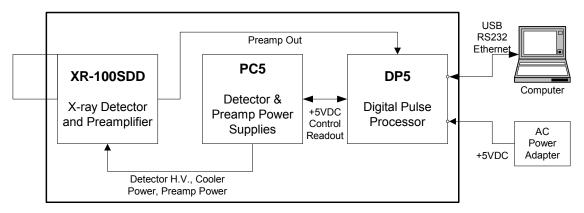

## 4.3 **DP5 WITH PC5**

The DP5 and PC5 can be used with Amptek's family of detectors and preamplifiers. It is appropriate for OEM use in a larger system.

The key points for this system are essentially the same as discussed above with the X123 and with the DP5. As in prior systems, Amptek has several different OEM preamplifiers which are electrically equivalent to the XR100 family but have different form factors for mounting in OEM sensor assemblies.

Amptek Inc. Page 17 of 39

- The PC4-3's primary interface was via an 8 pin connector which included power in, RS232 signals, and power control. The PC5 retains the same 8 pin connector, with the same location and pinout.

- Mounting holes and connector locations are unchanged. The boards are 62 mil shorter.

- The primary difference is in control, discussed below in the software migration section. In the PC4-3, high voltage bias and temperature set point were controlled via resistors or pots, usually set at the factory. They are now under software control and can be readout via ADCs. The control of these is like the control previously available in the PX4. For users with legacy software written for the DP4, these set points can be sent once in the PC5 and then stored in the DP5 EEPROM. After that, legacy DP4 code will function normally. Alternately, a user can modify code to support the DP5 and have full software control over these parameters.

- The PC5 can be delivered with either a positive or negative HV supply, and preamp supplies of either +/-5V, or +/-8.5V. These are set by jumpers (zero ohm resistors soldered on the board) so are not under software control.

# Block Diagram

Figure 9. Block diagram of DP5/PC5 system.

Figure 10. DP5/PC5 stack.

## 5. SOFTWARE MIGRATION

# 5.1 OVERVIEW

The DP5's software interface is very similar to that of the DP4 and PX4 and supports legacy software written for the older products. This document is intended to describe only the changes to the interface and assumes the user is familiar with the older software, documented elsewhere.

Amptek Inc. Page 18 of 39

For lab users, Amptek recommends the use of the ADMCA software package. One can now select the "DP5" from the pulldown menu and gain access to all of the DP5's features without going into the low level details described later in this document. For OEMs using their own software, it will be necessary to understand how the DP5 is configured and the changes which have been made to the data packets. OEMs and custom user ahouls use the DPP API when writing custom code in Windows. The advanced programming and low-level discussion later in this document is intended for user that want to write their own drivers, or are on a non-Windows platform.

This document applies to release FW 5.03 of the firmware and embedded software, which is the first production release. Additional features will be implemented in future releases. Users will be able to download the new releases from Amptek's website and program their DP5s in the field. Section 5.8 tells how to upload new releases.

# 5.1.1 Configuring the DP5

The DP5's configuration parameters are a superset of those found in the PX4, which is a superset of those found in the DP4. The DP4 has the minimum parameters (peaking time, MCA channels, etc). The PX4 includes these plus others such as detector HV bias, TEC temperature, and input polarity. The DP5 includes all of these plus additional parameters such as ADC clock rate. To provide backward compatibility with legacy software the DP5 handles these three classes of parameters quite differently.

The DP4 and PX4 use the same configuration data packets; the DP4 simply ignores the additional parameters which control options not available in the DP4 hardware. For backward compatibility, the DP5 recognizes the configuration packets of either the DP4 or the PX4, operating in a "DP4 emulation mode" or a "PX4 emulation mode. Since it needs all the parameters to operate properly, it reads the additional parameters from nonvolatile memory. These must be set via a new data packet, after which legacy software may be used. Some critical things to note are:

- 1. The new configuration options not available with either the DP4 or the PX4 are termed "boot flags," and are set via a new data packet and stored in EEPROM in the DP5.

- a. One important "boot" parameter sets whether the DP5 is in "DP4 emulation mode" or "PX4 emulation mode" In "PX4 emulation mode," the user can command the HV bias, temperature for the cooler, etc. In "DP4 emulation mode," the DP5 reads these from nonvolatile memory. [ADMCA requires the 'PX4 emulation mode,' and will switch the DP5 to that mode upon connection, if necessary.]

- b. Other boot parameters set the ADC clock frequency, the RS232 baud rate, etc.

- c. These boot parameters are set via USB, using either a "Boot Manager" provided by Amptek or by customer written software. ADMCA can set the boot flags as well.

- 2. Some of the configuration parameters have a different meaning in the DP5 and the meaning may depend on the boot options. For example, the coarse gain settings of the DP5 are different from either DP4 or PX4. In addition, as a boot option one can set the ADC clock to either 20 MHz or 80 MHz, and this will change the peaking time settings (the same configuration byte will lead to a peaking time which differs by a factor of four). The details are in section 5.2 of this document.

## 5.1.2 Data From the DP5

The DP4 and PX4 provide four data packet types:

- The spectral data packets are unchanged from the DP4/PX4.

- The status packet has several additional parameters, placed into bytes not used with the DP4 or PX4. In addition, some parameters have been redefined. Note: The status packet indicates if the device is a DP4, PX4, DP5 in "DP4 emulation mode", or DP5 in "PX4 emulation mode".

- The configuration readback packet works the same as the PX4/DP4. It will return the PX4/DP4

configuration packet most recently received by the DP5. Configuration readback over USB now

operates on a different USB pipe, as discussed elsewhere.

- The oscilloscope data shares USB Pipe 3 with the configuration readback, as described in Section 5.3.

Amptek Inc. Page 19 of 39

• The DP5 can store up to 512 bytes of miscellaneous data (text or binary) in nonvolatile memory, which is also read back via USB Pipe 3. The data is sent using 'USB Vendor Requests' as discussed later.

# 5.1.3 DP5 Buffering

The DP5 uses an improved technique to greatly reduce MCA deadtime associated with the readout of spectral data. The MCA memory in which the spectrum is acquired is internal to the FPGA. When the spectral data is requested, the MCA is disabled, and a high-speed hardware sequencer copies the spectral data to an external SRAM, simultaneously clearing the MCA memory if required. The MCA is then re-enabled and can continue to acquire data while the buffered spectrum is sent out.

The desired compatibility with the existing DP4 and PX4 protocols makes it difficult to use these new features in the ideal manner. For example, the sequencer that copies the spectral data can also simultaneously zero it, but only if it is configured to do so at the start of the transfer. With the existing USB protocol, it isn't known whether to zero the data until the transfer is complete. The net result is that for repetitive measurements, unnecessary deadtime is introduced. An extension to the protocol will be added to fix this in the next release of the firmware. The details of how this works are a bit different for USB vs. RS232, and are discussed below.

USB

Because of a limitation in the USB implementation in the DP5 microcontroller relative to that of the DP4 microcontroller, the DP5 USB buffering can't behave exactly the same way as the DP4. The DP4/PX4 use the initiation of a USB IN request (i.e. DP5 to PC host) as a trigger to buffer fresh data, and to start sending it immediately. The DP5 microcontroller lacks the ability to detect the initiation of an IN request (it only detects the completion), and thus can't work the same way as the DP4/PX4.

The solution is the use of USB retries as a mechanism for the DP5 to detect the start of an IN transfer. When the application requests data from one of the IN pipes (IN1=status; IN2=spectrum; IN3=configuration readback/oscilloscope data/misc data), the DP5 will immediately return a packet of length = 0. (The USB specification refers to this as a zero-length packet, or ZLP, and uses a ZLP to terminate a transfer.) The DP5 detects this transaction, and immediately fills the USB buffer with fresh data. The application should detect that the first attempt returned 0 bytes, and should immediately retry the request. The 2<sup>nd</sup> attempt will return the correct data. [Users of the DPPAPI won't need to worry about this – an updated version of the DLL will handle it transparently.]

Additionally, the relationship between the spectral and status data is slightly different. With the DP4/PX4, status packets were always 'live' – they would take a snapshot of the current state of the acquisition. In the DP5, a status packet is created at the same instant that the spectral data is buffered, so that the spectral & status data are synchronized. The first status read after the spectrum is read will return a status packet that is perfectly synchronized with the spectral data which was already read. For any subsequent status reads, the data will be "live", i.e. a new snapshot of status data is taken the instant the request is received by the DP5. Status packets will remain "live" until the next spectrum read, at which point a new synchronized status packet is generated, to be used for the first status read after the spectrum is read. [This isn't much different than the DP4/PX4. In the DP4/PX4, the spectrum and status data become synchronized (and static) after the acquisition ends (a preset expires, etc.) but there may be a bit of skew between them for intermediate reads.]

The following deadtimes due to USB communication were measured. The deadtime depends on the FPGA clock speed (20 or 80 MHz). There is an additional deadtime penalty if the spectrum is being cleared after it is read out – the time quoted below is the actual time the MCA is disabled to clear the spectrum. In reality, this additional deadtime includes the time between the spectrum being read out over USB, and the receipt of the USB command to clear the spectrum. [This time would depend on the host PC and amount of USB traffic, and is likely in the 5-10mS range.] This additional deadtime will be eliminated with the use of the protocol extension mentioned above.

| # of MCA channels selected | FPGA clock = 20MHz | FPGA clock = 80MHz |

|----------------------------|--------------------|--------------------|

| 256                        | 240uS              | 124uS              |

| 512                        | 431uS              | 200uS              |

| 1024                       | 815uS              | 354uS              |

| 2048                       | 1.58mS             | 661uS              |

Amptek Inc. Page 20 of 39

| 4096                    | 3.12mS | 1.28mS |

|-------------------------|--------|--------|

| 8192                    | 6.19mS | 2.50mS |

| Time for spectrum clear | 415uS  | 105uS  |

#### RS232

The RS232 protocol used by the DP4/PX4 can be used unmodified with the DP5. [The boot flags must be set to the proper baud rate: 57.6k or 115.2k, as documented below. The DP4/PX4 has a fixed baud rate of 57.6k.] . With the use of protocol extensions for the DP5, RS232 deadtimes similar to the USB deadtimes discussed above can be expected.

The RS232 data request packet consists of a sync byte, requested packet number, and end of packet byte (this is the same as the DP4/PX4 data request):

# Data request packet (3 bytes):

| Byte 1 | 0xFD (sync)                  |  |

|--------|------------------------------|--|

| Byte 2 | requested packet number      |  |

| Byte 3 | 0xFF (end of packet request) |  |

Previously, any RS232 data request resulted in 256 bytes being returned. The DP5 adds several protocol extensions which allow a single request to result in the entire data set being returned: the spectrum, status and configuration packet.

| Function                                    | Request packet number |  |

|---------------------------------------------|-----------------------|--|

| Request entire data set                     | 0x65                  |  |

| Request entire data set plus Clear Spectrum | 0x66                  |  |

The amount of data generated by the 'Request Entire Data Set...' commands depends on how many MCA channels are currently selected. The data set consists of spectral data (768, 1536, 3072, 6144, 12288 or 24576 bytes), followed by the 64-byte status packet and ending with a 64-byte packet reflecting the current configuration.

The spectral data is 3 bytes/channel (LSB to MSB), going from lowest channel to highest channel. The 64 bytes of status data immediately follow the spectral data, and its format is discussed later. The final 64 bytes is the current configuration, and its format is the same as the configuration packet, also described later. The following table shows the structure of the data returned by the 'Request Entire Data Set...' commands:

| # of Channels | Total Data Returned | Spectral Data | Status Data       | Configuration Data |

|---------------|---------------------|---------------|-------------------|--------------------|

| 256           | 896 bytes           | Bytes 0-767   | Bytes 768-831     | Bytes 832-895      |

| 512           | 1664 bytes          | Bytes 0-1535  | Bytes 1536-1599   | Bytes 1600-1663    |

| 1024          | 3200 bytes          | Bytes 0-3071  | Bytes 3072-3135   | Bytes 3136-3199    |

| 2048          | 6272 bytes          | Bytes 0-6143  | Bytes 6144-6207   | Bytes 6208-6271    |

| 4096          | 12416 bytes         | Bytes 0-12287 | Bytes 12288-12351 | Bytes 12352-12415  |

| 8192          | 24704 bytes         | Bytes 0-24575 | Bytes 24576-24639 | Bytes 24640-24703  |

# 5.2 Changes to Configuration Packets

# 5.2.1 Boot Configuration ("Boot Flags")

This table shows the "boot flags", which are recognized only by the DP5. These values can only be sent via USB vendor requests, in the initial firmware release (FW 5.03). Most of these values are true boot options so only take effect on reset. The exceptions are noted as "live" in the table below. "Live" options will take effect when the next configuration packet is received by the DP5.

This table defines the individual bits of the 16-bit value field of the Vendor Request. All undefined bits should be regarded as "reserved" and should be set to 0. Note: the MSB bits (bits D15-D8) are volatile; they all

Amptek Inc. Page 21 of 39

default to 0 at power-up. The LSB bits (bits D7-D0) are non-volatile, and are restored to their commanded state at power-up.

| Bit         | Val | Description                                                                                                                                                                                                              |

|-------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D15-<br>D10 | 0   | Currently unused                                                                                                                                                                                                         |

| D9          | 0   | MCA source: Slow channel (normal operation):                                                                                                                                                                             |

|             | 1   | MCA source: Fast channel. Sets the source for the MCA to the fast channel. Note that the fast channel does not have BLR or a pole-zero.                                                                                  |

| D8          | 0   | Peak detect: Max only (normal operation)                                                                                                                                                                                 |

|             | 1   | Max and min: Allows the peak detect (and MCA) to capture local minima of the shaped pulse stream, in addition to local maxima. Primary use is for capturing the 'noise Gaussian' for determining the true spectrum zero. |

| D7          | 0   | PX4 emulation mode (use PX4 parameters, reports 'PX4' in status)                                                                                                                                                         |

|             | 1   | DP4 emulation mode (use nonvolatile HV & cooler parameters; report 'DP4' status)                                                                                                                                         |

| D6          | 0   | Boot in unconfigured state                                                                                                                                                                                               |

|             | 1   | Use nonvolatile configuration, report 'power button config' in status. Equivalent to "holding the power button until the second beep" in PX4.                                                                            |

| D5          | 0   | 57,600 baud for RS232. Used in legacy units.                                                                                                                                                                             |

|             | 1   | 115,200 baud                                                                                                                                                                                                             |

| D4          | 0   | 20MHz FPGA clock. Used in the legacy units. This parameter is "live".                                                                                                                                                    |

|             | 1   | 80MHz FPGA clock. Provides faster peaking times to operate at higher count rates.                                                                                                                                        |

| D3          | 0   | Negative HV PC5 required                                                                                                                                                                                                 |

|             | 1   | Positive HV PC5 required                                                                                                                                                                                                 |

| D2          | 0   | Positive pulse input to DP5, i.e. SDD [DP4 emulation mode only; use 'invert' bit in PX4 emulation mode]                                                                                                                  |

|             | 1   | Negative pulse input to DP5, i.e. XR100 [" "]                                                                                                                                                                            |

| D1          | 0   | Use spectrum offset of 0. This parameter is "live".                                                                                                                                                                      |

|             | 1   | Use spectrum offset as programmed via boot option                                                                                                                                                                        |

| D0          | 0   | Normal fast channel peaking time (400nS @ 20MHz clock, 100nS @ 80MHz)                                                                                                                                                    |

|             | 1   | 4x slower fast channel peaking time (1.6uS @ 20MHz clock, 400nS @ 80MHz)                                                                                                                                                 |

## Notes

- ADMCA always uses "PX4 emulation mode". If ADMCA connects to a DP5 and finds it in "DP4 emulation mode", then it will send the command to change emulation mode and will then instruct the user to reboot the DP5 before proceeding.

- The "DP4 emulation mode" is intended only for use to support legacy applications and software. In this case, use the boot manager to set the mode and the options.

High Voltage Polarity: The legacy power supplies only had a positive bias available. The new PC5 power supply can be configured for negative polarity, by setting jumpers on the board. The DP5 checks the jumper settings before enabling any supplies on the PC5. Setting this bit does not change the supply polarity; it tells the DP5 which polarity is required before applying power.

NOTE: Applying the incorrect polarity may permanently damage a detector.

Amptek Inc. Page 22 of 39

• Flags D4 (FPGA clock) and D1 (spectrum offset) are "live" - they take effect immediately without rebooting the DP5.

# 5.2.2 Changes to Standard Configuration Packet

This table shows the "standard configuration packet", which is recognized by the DP4, the PX4, and the DP5. These values can be sent via RS232 or USB. The CLK\_FAC equals 1 for 20 MHz ADC and 4 for 80 MHZ ADC.

| Offset | Data<br>bits | Allowed<br>Value | Description                                                                              | DP5 Changes                                                                                                                       |

|--------|--------------|------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 0      | D7           | 0                | 0=Normal reset lockout, 1=fast reset lockout                                             |                                                                                                                                   |

|        | D6-D3        | t=015            | Flat top width=200nS*(t+1)*2 <sup>d</sup>                                                | Scales with ADC clock but otherwise same. See Table 2. (200nS/CLK_FAC)*(t+1)*2 <sup>d</sup>                                       |

|        | D2-D0        | d=04             | Decimation factor=2 <sup>d</sup>                                                         |                                                                                                                                   |

| 1      | D7-D0        | 0255             | Slow channel threshold                                                                   |                                                                                                                                   |

| 2      | D7-D0        | 0255             | Fast channel threshold                                                                   | Still set the same way but optimum setting will depend on fast channel peaking time, which depends on ADC clock. See section 3.2. |

| 3      | D7-D1        | -64+63           | Output DAC offset (signed) (-500mV to +492mV)                                            |                                                                                                                                   |

|        | D0           | 0                | DAC disabled                                                                             |                                                                                                                                   |

|        |              | 1                | DAC enabled                                                                              |                                                                                                                                   |

| 4      | D7-D6        | 0                | normal operation                                                                         |                                                                                                                                   |

|        | D5           | 0                | MCA disabled                                                                             |                                                                                                                                   |

|        |              | 1                | MCA enabled                                                                              |                                                                                                                                   |

|        | D4-D2        | 0                | MCA/MCS 4096 channel mode                                                                |                                                                                                                                   |

|        |              | 1                | MCA/MCS 2048 channel mode                                                                |                                                                                                                                   |

|        |              | 2                | MCA/MCS 1024 channel mode                                                                |                                                                                                                                   |

|        |              | 3                | MCA/MCS 512 channel mode                                                                 |                                                                                                                                   |

|        |              | 4                | MCA/MCS 256 channel mode                                                                 |                                                                                                                                   |

|        |              | 5                | MCA/MCS 8192 channel mode                                                                |                                                                                                                                   |

|        | D1-D0        | 0                | DAC output=fast channel                                                                  |                                                                                                                                   |

|        |              | 1                | DAC output=shaped pulse                                                                  |                                                                                                                                   |

|        |              | 2                | DAC output=decimated input                                                               |                                                                                                                                   |

|        |              | 3                | DAC output= Test Pulser                                                                  |                                                                                                                                   |

| 5      | D7-D0        | 1255             | Pileup Reject interval: optimal setting is (p * 19 + (t + 1) * 4) / 2                    | Not used in new pile-up reject logic – PUR is enabled for any nonzero value. See section 3.3.                                     |

|        |              | 0                | Pileup Reject disabled                                                                   | Disable is still used as before.                                                                                                  |

| 6      | D7-D4        | p=18             | Peaking Time=800nS*p*2 <sup>d</sup> (See Config byte 0: bits D2-D0, and also Table 2.    | Scales with ADC clock but otherwise same. See Table 2. (800nS/CLK_FAC)* p*2 <sup>d</sup>                                          |

|        | D3-D2        | 0                | Detector reset lockout period=13.11mS (slow) or 819uS (fast) (see Config byte 0: bit D0) | Lockout period reduced by                                                                                                         |

|        |              | 1                | Detector reset lockout period=6.55mS or 410uS                                            | CLK_FAC                                                                                                                           |

|        |              | 2                | Detector reset lockout period=3.28mS or 205uS                                            |                                                                                                                                   |

|        |              | 3                | Detector reset lockout period=1.64mS or 102uS                                            |                                                                                                                                   |

|        | D1           | 0                | No auto baseline reset during detector reset                                             | Autobaseline replaced by BLR.                                                                                                     |

|        |              | 1                | Auto baseline reset during detector reset                                                | This bit is reserved in FW 5.03 and should be set to 0.                                                                           |

|        | D0           | 0                | Disable MCA during detector reset                                                        |                                                                                                                                   |

Amptek Inc. Page 23 of 39

|    |              | Ι.    |                                               | al Flocessor Migration Guide Nev 64                                                    |

|----|--------------|-------|-----------------------------------------------|----------------------------------------------------------------------------------------|

|    |              | 1     | Do not disable MCA during detector reset      |                                                                                        |

| 7  | D7-D0        | 0255  | RTD slow threshold                            | This is the 8-bit RTD sensitivity setting, similar to the DP4/PX4 'RTD Time Threshold' |

| 8  | D7           | 1     | Normal operation                              |                                                                                        |

|    | D6           | 0     | (Reserved)                                    |                                                                                        |

|    | D5           | 0-1   | Analog gain control A (SeeTable 1.)           | New gain table. See Table 1                                                            |

|    | D4           | 0     | RTD off                                       | 146W gain table. Coc rable 1                                                           |

|    |              | 1     | RTD on                                        |                                                                                        |

|    | D3-D0        | 015   | RTD time threshold                            | This 4-bit setting is now the RTD slow threshold: 15=50% full-scale                    |

| 9  | D7           | 0     | 50% digital attenuation                       |                                                                                        |

|    |              | 1     | Normal operation                              |                                                                                        |

|    | D6           | 0     | 0=Baseline Restoration (BLR) off              |                                                                                        |

|    |              | 1     | BLR enabled                                   |                                                                                        |

|    | D5-D4        | 0     | BLR Down correction=very slow                 |                                                                                        |

|    |              | 1     | BLR Down correction=slow                      | These essentially set the slew rate                                                    |

|    |              | 2     | BLR Down correction=medium                    | of the BLR correction. Changing                                                        |

|    |              | 3     | BLR Down correction=fast                      | the clock rate increases the slew for                                                  |

|    | D3-D2        | 0     | BLR Up correction=very slow                   | the same setting: a BLR down of "medium" at 20 MHz will produce                        |

|    |              | 1     | BLR Up correction=slow                        | the same slew as "slow" at 80 MHz.                                                     |

|    |              | 2     | BLR Up correction=medium                      |                                                                                        |

|    |              | 3     | BLR Up correction=fast                        |                                                                                        |

|    | D1-D0        | 0     | BLR correction threshold=very fast            | The new algorithm fixes the                                                            |

|    | 3.50         | 1     | BLR correction threshold=fast                 | threshold at "Very Fast". This                                                         |

|    |              | 2     | BLR correction threshold=normal               | parameter is no longer adjustable.                                                     |

|    |              | 3     | BLR correction threshold=slow                 | <del>-</del>                                                                           |

| 10 | D7-D6        | 0     | GATE off                                      | The DP5 uses the 'AUX IN1' signal                                                      |

| 10 | <i>D7 D0</i> | 1     | N/A (Gate off)                                | for GATE, "Active high" means                                                          |

|    |              | 2     | GATE on, polarity active high                 | events are passed when the                                                             |

|    |              | 3     | GATE on, polarity active low                  | - 'AUX_IN1' input is low, and events                                                   |

|    | D= D4        |       | * * * * * * * * * * * * * * * * * * * *       | are gated off when it is high.                                                         |

|    | D5-D4        | 0     | Software MCA buffer select, buffer A          | The DP5 does not support buffer B so these bits are "reserved".                        |

|    |              | 1     | Software MCA buffer select, buffer B          | So these bits are reserved.                                                            |

|    |              | 2     | Hardware MCA buffer select                    |                                                                                        |

|    |              | 3     | N/A                                           |                                                                                        |

|    | D3           | 0     | Digital scope trigger = rising edge           |                                                                                        |

|    |              | 1     | Digital scope trigger = falling edge          |                                                                                        |

|    | D2-D0        | 0     | AUX_OUT=ICR                                   |                                                                                        |

|    |              | 1     | AUX_OUT=PILEUP                                |                                                                                        |

|    |              | 2     | AUX_OUT=MCS_TIMEBASE                          |                                                                                        |

|    |              | 3     | AUX_OUT=ONESHOT                               |                                                                                        |

|    |              | 4     | AUX_OUT=DET_RES (active low)                  |                                                                                        |

|    |              | 5     | AUX_OUT=MCA_EN                                |                                                                                        |

|    |              | 6     | AUX_OUT=TRIGGER                               |                                                                                        |

|    |              | 7     | AUX_OUT=SCA8                                  |                                                                                        |

| 11 | D7-D0        | 0-255 | Preset time LSB                               |                                                                                        |

| 12 | D7-D0        | 0-255 | Preset time Byte2                             |                                                                                        |

| 13 | D7-D0        | 0-255 | Preset time MSB                               |                                                                                        |

|    |              |       | [Time=0.1 sec<br>[MSB*(2^16)+Byte2*(2^8)+LSB] | *                                                                                      |

Note 1: These parameters do nothing in FW 5.03; they are ignored. Future releases will use them as in the DP4 and PX4.

Amptek Inc. Page 24 of 39

| r               | ,                |          | igital i loc |

|-----------------|------------------|----------|--------------|

| Analog Gain     | Analog Gain      |          |              |

| Control A       | Control B        |          |              |

| (Config byte 8, | (Config byte 15, | PX4 Gain | DP5 Gain     |

| bit D5)         | bits D3-D0)      |          |              |

| 1               | 0                | 4.13     | 3.78         |

| 1               | 1                | 4.95     | 5.26         |

| 1               | 2                | 5.94     | 6.56         |

| 1               | 3                | 7.17     | 6.56         |

| 0               | 0                | 8.22     | 8.39         |

| 0               | 1                | 9.84     | 10.10        |

| 0               | 2                | 11.80    | 11.31        |

| 0               | 3                | 14.30    | 14.56        |

| 1               | 4                | 17.50    | 17.77        |

| 1               | 5                | 20.90    | 22.42        |

| 1               | 6                | 25.10    | 22.42        |

| 1               | 7                | 30.30    | 30.83        |

| 0               | 4                | 34.70    | 38.18        |

| 0               | 5                | 41.60    | 38.18        |

| 0               | 6                | 49.90    | 47.47        |

| 0               | 7                | 60.30    | 66.26        |

| 0               | 8                | 76.70    | 66.26        |

| 0               | 9                | 91.90    | 102.01       |

| 0               | 10               | 110.00   | 102.01       |

| 0               | 11               | 133.00   | 102.01       |

| 1               | 12               | 163.00   | 102.01       |

| 1               | 13               | 195.00   | 102.01       |

| 1               | 14               | 234.00   | 102.01       |

| 1               | 15               | 283.00   | 102.01       |

| 0               | 12               | 324.00   | 102.01       |

| 0               | 13               | 388.00   | 102.01       |

| 0               | 14               | 466.00   | 1.00         |

| 0               | 15               | 563.00   | 2.22         |

Table 1. Gain settings in the PX4 and the DP5. Note that the DP5 has a slightly different gain range.

| 20 MHz               | MHz Clock 80 MHz Clock |                      |                  |            |                    |                      |                     |

|----------------------|------------------------|----------------------|------------------|------------|--------------------|----------------------|---------------------|

| Peaking<br>Time (μS) | Flat Top<br>(μS)       | Peaking<br>Time (μS) | Flat Top<br>(μS) | Decimation | 'Rise'<br>register | Flat Top<br>register | Decimation register |

| 0.8                  | 0.23.2                 | 0.2                  | 0.050.8          | 1          | 1                  | 015                  | 0                   |

| 1.6                  | 0.23.2                 | 0.4                  | 0.050.8          | 1          | 2                  | 015                  | 0                   |