PHOTON IS OUR BUSINES

# **Distance linear image sensor**

S15452-01WT

# NIR-enhanced type, measures the distance to an object by TOF method

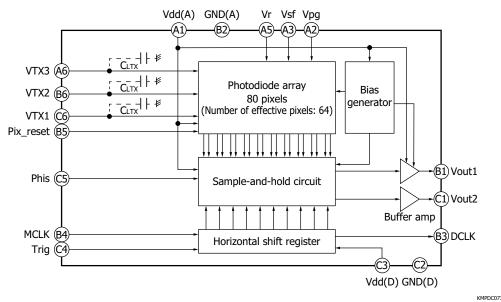

The distance image sensor is designed to measure the distance to an object by TOF (time-of-flight) method. When used in combination with a pulse modulated light source, this sensor outputs phase difference information on the timing that the light is emitted and received. Distance data can be obtained by performing calculation on the output signal with an external signal processing circuit or on a PC. We provide an evaluation kit for this product. Contact us for detailed information.

#### Features

- High sensitivity in the near infrared region

- Improved tolerance to background light

- Number of effective pixels: 64

- Compact chip size package (CSP) type

#### Applications

- **→** Obstacle detection (self-driving, robots, etc.)

- Security (intrusion detection, etc.)

- Shape recognition (logistics, robots, etc.)

- Motion capture

- **→** Touchless operation

#### Structure

| Parameter                  | Specification | Unit   |

|----------------------------|---------------|--------|

| Image size                 | 1.28 × 0.05   | mm     |

| Pixel pitch                | 20            | μm     |

| Pixel height               | 50            | μm     |

| Number of pixels           | 80            | pixels |

| Number of effective pixels | 64            | pixels |

| Package                    | CSP           | -      |

Note: This product is not hermetically sealed.

#### - Absolute maximum ratings

|                               | Parameter                                       | Symbol           | Condition             | Value                | Unit |

|-------------------------------|-------------------------------------------------|------------------|-----------------------|----------------------|------|

| Analog supply vo              | oltage                                          | Vdd(A)           | Ta=25 °C              | -0.3 to +4.2         | V    |

| Digital supply vo             | oltage                                          | Vdd(D)           | Ta=25 °C              | -0.3 to +4.2         | ٧    |

| Analog input                  | Pixel amplifier                                 | Vsf              |                       |                      |      |

| Analog input terminal voltage | Pixel reset                                     | Vr               | Ta=25 °C              | -0.3 to Vdd(A) + 0.3 | V    |

| terriiriai voitage            | Photosensitive area                             | Vpg              |                       |                      |      |

|                               | Pixel reset pulse                               | Pix_reset        |                       |                      |      |

| District in mot               | Signal sampling pulse                           | Phis             |                       |                      |      |

| Digital input                 | Master clock pulse Signal readout trigger pulse | MCLK             | Ta=25 °C              | -0.3 to Vdd(D) + 0.3 | V    |

| terrimai voitage              | Signal readout trigger pulse                    | Trig             |                       |                      |      |

|                               | Output signal sync pulse                        | DCLK             |                       |                      |      |

| Charge transfer               | clock pulse voltage                             | VTX1, VTX2, VTX3 | Ta=25 °C              | -0.3 to Vdd(A) + 0.3 | V    |

| Operating temperating         | erature                                         | Topr             | No dew condensation*1 | -25 to +85           | °C   |

| Storage tempera               | ature                                           | Tstg             | No dew condensation*1 | -40 to +85           | °C   |

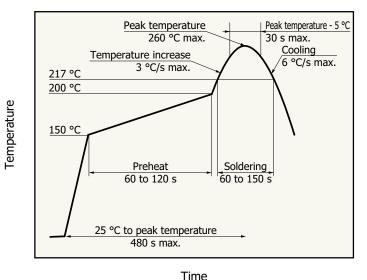

| Soldering tempe               | erature*2                                       | Tsol             |                       | 260 (twice)          | °C   |

<sup>\*1:</sup> When there is a temperature difference between a product and the surrounding area in high humidity environment, dew condensation may occur on the product surface. Dew condensation on the product may cause deterioration in characteristics and reliability.

<sup>\*2:</sup> Reflow soldering, IPC/JEDEC J-STD-020 MSL 2, see P.9

Note: Exceeding the absolute maximum ratings even momentarily may cause a drop in product quality. Always be sure to use the product within the absolute maximum ratings.

#### ■ Recommended terminal voltage (Ta=25 °C)

| Parameter                  |                       | Symbol    | Min.                | Тур.   | Max.                | Unit |  |

|----------------------------|-----------------------|-----------|---------------------|--------|---------------------|------|--|

| Analog supply voltage      | Analog supply voltage |           | 3.2                 | 3.3    | 3.4                 | V    |  |

| Digital supply voltage     |                       | Vdd(D)    | 3.2                 | 3.3    | 3.4                 | V    |  |

|                            | Pixel amplifier       | Vsf       | -                   | Vdd(A) | -                   | V    |  |

| Bias voltage               | Pixel reset           | Vr        | 2.5                 | 2.6    | 2.7                 | V    |  |

|                            | Photosensitive area   | Vpg       | 0.6                 | 0.8    | 1.0                 | V    |  |

| Pixel reset pulse voltage  | High level            | Div rocot | $Vdd(D) \times 0.8$ | -      | -                   | V    |  |

| Pixel reset pulse voltage  | Low level             | Pix_reset | -                   | -      | $Vdd(D) \times 0.2$ | V    |  |

| Signal sampling pulse      | High level            | Phis      | $Vdd(D) \times 0.8$ | -      | -                   | V    |  |

| voltage                    | Low level             | FIIIS     | -                   | -      | $Vdd(D) \times 0.2$ |      |  |

| Master clock pulse voltage | High level            | MCLK      | $Vdd(D) \times 0.8$ | -      | -                   | W    |  |

| Master Clock pulse voltage | Low level             | MCLK      | -                   | -      | $Vdd(D) \times 0.2$ | V    |  |

| Signal readout trigger     | High level            | Trig      | $Vdd(D) \times 0.8$ | -      | -                   | V    |  |

| pulse voltage              | Low level             | ilig      | -                   | -      | $Vdd(D) \times 0.2$ | V    |  |

| Output signal sync pulse   | High level            | DCLK      | $Vdd(D) \times 0.8$ | -      | -                   | V    |  |

| voltage                    | Low level             | DCLK      | -                   | -      | $Vdd(D) \times 0.2$ | V    |  |

#### Electric characteristics [Ta=25 °C, Vdd(A)=Vdd(D)=3.3 V]

| Parameter             | Symbol  | Condition  | Min. | Тур.    | Max. | Unit |

|-----------------------|---------|------------|------|---------|------|------|

| Clock pulse frequency | f(MCLK) |            | 1 M  | -       | 5 M  | Hz   |

| Data rate             | DR      |            | -    | f(MCLK) | -    | Hz   |

| Current consumption   | Ic      | Dark state | -    | 6       | -    | mA   |

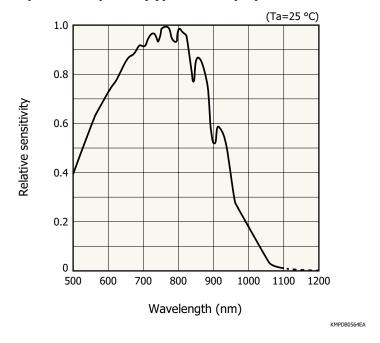

#### **Electrical and optical characteristics** [Ta=25 °C, Vdd(A)=Vdd(D)=3.3 V, Vsf=3.3 V, Vr=2.6 V, MCLK=5 MHz]

| Parameter                     | Symbol | Min. | Тур.                 | Max. | Unit    |

|-------------------------------|--------|------|----------------------|------|---------|

| Spectral response range       | λ      |      | 500 to 1100          |      | nm      |

| Peak sensitivity wavelength   | λр     | -    | 800                  | -    | nm      |

| Photosensitivity*3            | S      | -    | $1.4 \times 10^{12}$ | -    | V/(W·s) |

| Dark output                   | Vd     | -    | 2.8                  | 5    | V/s     |

| Random noise                  | RN     | -    | 0.5                  | 1    | mV rms  |

| Dark output voltage*4         | Vor    | -    | 2.7                  | -    | V       |

| Sensitivity ratio*5           | SR     | 0.7  | -                    | 1.43 | -       |

| Photoresponse nonuniformity*6 | PRNU   | -    | -                    | ±10  | %       |

<sup>\*3:</sup> Monochromatic wavelength light source ( $\lambda$ =805 nm)

PRNU= $\Delta X/X \times 100$  [%]

X: average of the output of all pixel,  $\Delta X$ : difference between the maximum or minimum output and X

<sup>\*4:</sup> Output value right after reset in dark state

<sup>\*5:</sup> Output ratio of Vout1 (VTX1=1.8 V, VTX2=VTX3=0 V) to Vout2 (VTX2=1.8 V, VTX1=VTX3=0 V)

<sup>\*6:</sup> Photoresponse nonuniformity (PRNU) is the output nonuniformity that occurs when the entire photosensitive area is uniformly illuminated by light which is 50% of the saturation exposure level. PRNU is measured using 64 pixels excluding 8 pixels each at both ends, and is defined as follows.

#### Spectral response (typical example)

#### Block diagram

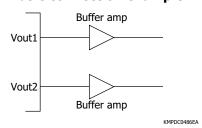

#### **Basic connection example**

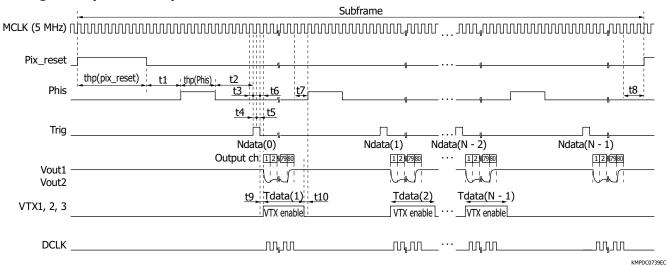

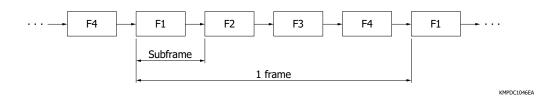

#### Timing chart (subframe\*7)

\*7: Data with different phase timing. One frame consists of four subframes (F1, F2, F3, F4).

#### ■ Phase timing of VTX enable

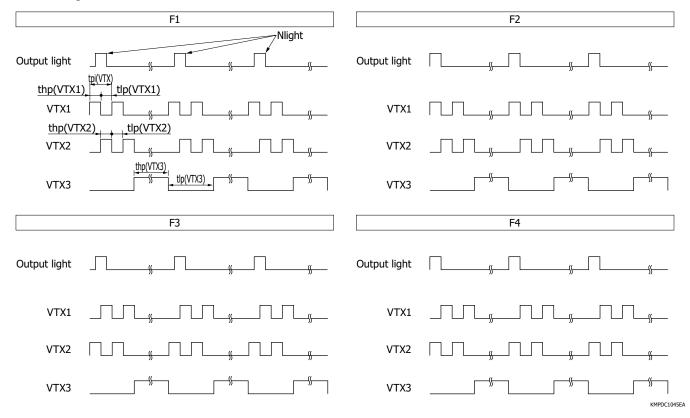

#### ■ Specifications of I/O signals

KMPDC0740ED

### S15452-01WT

| Davameter                                                                                                                          |              | Cumhal                       | Min             | Tim                                | May             | Linit     |

|------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------------|-----------------|------------------------------------|-----------------|-----------|

| Parameter                                                                                                                          |              | Symbol                       | Min.            | Тур.                               | Max.            | Unit<br>% |

| Master clock pulse duty ratio                                                                                                      |              | -                            | 45              | 50                                 | 55              |           |

| Master clock pulse rise and fall times*8                                                                                           |              | tr(MCLK), tf(MCLK)           | 0               | -                                  | 20              | ns        |

| Pixel reset pulse high period                                                                                                      |              | thp(Pix_reset)               | 10              | -                                  | -               | μs        |

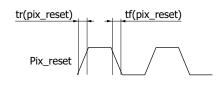

| Pixel reset pulse rise and fall times*8                                                                                            |              | tr(Pix_reset), tf(Pix_reset) |                 | -                                  | 20              | ns        |

| Signal sampling pulse high period                                                                                                  |              | thp(Phis)                    | 1               | -                                  | -               | μs        |

| Signal sampling pulse rise and fall times*                                                                                         |              | tr(Phis), tf(Phis)           | 0               | -                                  | 20              | ns        |

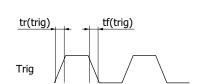

| Signal readout trigger pulse rise and fall t                                                                                       |              | tr(Trig), tf(Trig)           | 0               | -                                  | 20              | ns        |

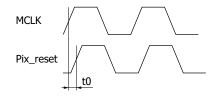

| Time from rising edge of master clock pu edge of pixel reset pulse                                                                 |              | t0                           | 0               | -                                  | -               | ns        |

| Time from falling edge of pixel reset puls of signal sampling pulse                                                                |              | t1                           | 1               | -                                  | -               | μs        |

| Time from falling edge of signal sampling edge of signal readout trigger pulse                                                     |              | t2                           | 1.2             | -                                  | -               | μs        |

| Time from rising edge of master clock pu edge of signal readout trigger pulse                                                      | _            | t3                           | 1/4 × 1/f(MCLK) | -                                  | 1/2 × 1/f(MCLK) | S         |

| Time from rising edge of signal readout t rising edge of master clock pulse                                                        |              | t4                           | 1/4 × 1/f(MCLK) | -                                  | 1/2 × 1/f(MCLK) | S         |

| Time from rising edge of master clock pu edge of signal readout trigger pulse                                                      |              | t5                           | 1/4 × 1/f(MCLK) | -                                  | 1/2 × 1/f(MCLK) | S         |

| Time from falling edge of signal readout rising edge of master clock pulse                                                         |              | t6                           | 1/4 × 1/f(MCLK) | -                                  | 1/2 × 1/f(MCLK) | S         |

| Time from rising edge of master clock pulse (after reading signals from all pixels) to rising edge of output signal sampling pulse |              | t7                           | 1/f(MCLK)       | -                                  | -               | S         |

| Time from rising edge of master clock pulse (after reading signals from all pixels) to rising edge of pixel reset pulse            |              | t8                           | 1/f(MCLK)       | -                                  | -               | S         |

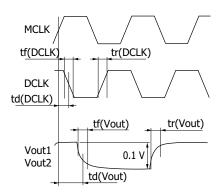

| Time from rising edge of master clock pulse to falling edge of output signal sync pulse*9                                          |              | td(DCLK)                     | -               | 7                                  | -               | ns        |

| Output signal sync pulse rise time*8 *9                                                                                            |              | tr(DCLK)                     | -               | 12                                 | -               | ns        |

| Output signal sync pulse fall time*8 *9                                                                                            |              | tf(DCLK)                     | -               | 8                                  | -               | ns        |

| Settling rise time of output signal 1, 2*8 *                                                                                       | *10          | tr(Vout)                     | -               | 20                                 | -               | ns        |

| Settling fall time of output signal 1, 2*8 *9                                                                                      | *10          | tf(Vout)                     | -               | 20                                 | -               | ns        |

| Time from rising edge of master clock pu signal 1, 2 (output 50%)*9                                                                | se to output | td(Vout)                     | -               | 18                                 | -               | ns        |

| Charge transfer clock pulse cycle                                                                                                  |              | tpi(VTX)                     | 60              | -                                  | -               | ns        |

|                                                                                                                                    | High period  | thp(VTX1)                    | 30              | -                                  | -               |           |

| Charge transfer clock pulse (VTX1)                                                                                                 | Low period   | tlp(VTX1)                    | -               | tpi(VTX)<br>thp(VTX2)<br>thp(VTX3) | -               | ns        |

|                                                                                                                                    | High period  | thp(VTX2)                    | 30              | -                                  | -               |           |

| Charge transfer clock pulse (VTX2)                                                                                                 | Low period   | tlp(VTX2)                    | -               | tpi(VTX)<br>thp(VTX1)<br>thp(VTX3) | -               | ns        |

|                                                                                                                                    | High period  | thp(VTX3)                    | 0               | -                                  | -               |           |

| Charge transfer clock pulse (VTX3)                                                                                                 | Low period   | tlp(VTX3)                    | -               | tpi(VTX)<br>thp(VTX1)<br>thp(VTX2) | -               | ns        |

| Charge transfer clock pulse voltage rise and fall times*8                                                                          |              | tr(VTX), tf(VTX)             | -               | 3                                  | -               | ns        |

| Charge transfer clock High level                                                                                                   |              |                              | 1.6             | 1.8                                | 2.0             | V         |

| Pulse voltage                                                                                                                      | Low level    | VTX1, VTX2, VTX3             | -               | 0                                  | -               | V         |

| Time from falling edge of signal readout start of VTX drive                                                                        |              | t9                           | 1/f(MCLK)       | -                                  | -               | S         |

| Time from end of VTX drive to rising edge signal sync pulse                                                                        | e of output  | t10                          | 1/f(MCLK)       | -                                  | -               | S         |

<sup>\*8: 10</sup> to 90%

\*9: Load capacitance CL=3 pF

\*10: Output voltage=0.1 V

#### Calculation method of frame rate

Frame rate=1/4 of subframe time

■ If the integration time is longer than the readout time

Time per subframe=Integration time × (Non-destructive readout count - 1) + Readout time

■ If the integration time is shorter than the readout time

Time per subframe=Readout time × Non-destructive readout time

Note: The integration time setting needs to be changed depending on the required distance accuracy and usage environment factors such as background light.

[Readout time calculation]

Readout time=

$$\frac{1}{\text{Clock pulse frequency}} \times \text{Number of horizontal pixels}$$

=Time per clock (Readout time per pixel) × Number of horizontal pixels

· Calculation example (clock pulse frequency=5 MHz, number of horizontal pixels=80)

Readout time=

$$\frac{1}{5 \times 10^6 \text{ [Hz]}} \times 80$$

= 200 [ns] × 80

= 0.016 [ms]

#### **■** Input terminal capacitance (Ta=25 °C, Vdd=3.3 V)

| Parameter                                             | Symbol | Min. | Тур. | Max. | Unit |

|-------------------------------------------------------|--------|------|------|------|------|

| Charge transfer clock pulse internal load capacitance | CLTX   | -    | 10   | -    | pF   |

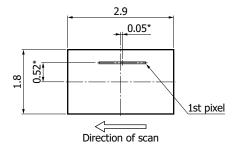

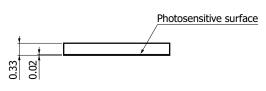

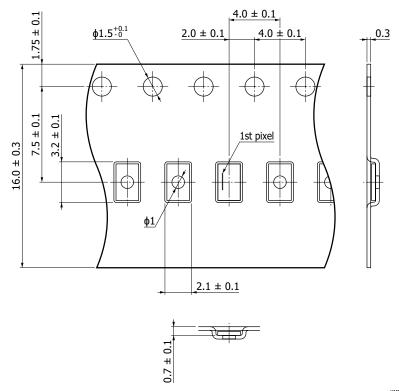

#### Dimensional outline (unit: mm)

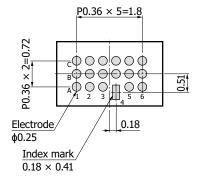

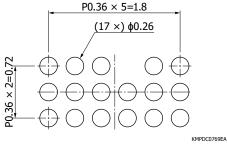

## Recommended land pattern (unit: mm)

Tolerance unless otherwise noted: ±0.1

Au electrode

\* Distance from package center to photosensitive area center

#### Pin connections

| Pin no. | Symbol    | I/O | Description                                                   |  |  |

|---------|-----------|-----|---------------------------------------------------------------|--|--|

| A1      | Vdd(A)    | I   | Analog supply voltage                                         |  |  |

| B1      | Vout1     | 0   | Output signal 1                                               |  |  |

| C1      | Vout2     | 0   | Output signal 2                                               |  |  |

| A2      | Vpg       | I   | Photosensitive area bias voltage                              |  |  |

| B2      | GND(A)    | I   | Ground                                                        |  |  |

| C2      | GND(D)    | I   | Ground                                                        |  |  |

| A3      | Vsf       | I   | Pixel amplifier drain voltage                                 |  |  |

| В3      | DCLK      | 0   | Output data sample clock                                      |  |  |

| C3      | Vdd(D)    | I   | Digital supply voltage                                        |  |  |

| A4      | NC        | -   | No connection                                                 |  |  |

| B4      | MCLK      | I   | Master clock input signal                                     |  |  |

| C4      | Trig      | I   | Signal readout trigger signal (reset and signal level)        |  |  |

| A5      | Vr        | I   | Pixel reset voltage                                           |  |  |

| B5      | Pix_reset | I   | Pixel reset pulse                                             |  |  |

| C5      | Phis      | I   | Signal sampling signal (level determined on the falling edge) |  |  |

| A6      | VTX3      | I   | Charge transfer clock 3 (for OFD)                             |  |  |

| B6      | VTX2      | I   | Charge transfer clock 2                                       |  |  |

| C6      | VTX1      | I   | Charge transfer clock 1                                       |  |  |

Note: Leave the NC terminals open.

Connect an impedance converting buffer amplifier to Vout1 and Vout2 terminals so as to minimize the current flow.

#### Reel packing specifications

■ Reel (conforms to JEITA ET-7200)

| Outer diameter | Hub diameter | Tape width | Material | Electrostatic characteristics |

|----------------|--------------|------------|----------|-------------------------------|

| φ180 mm        | φ60 mm       | 16 mm      | PS       | Conductive                    |

■ Embossed tape (unit: mm, material: PS, conductive)

- Packing quantity500 pcs/reel

- Packing stateReel and desiccant in moisture-proof packaging (vacuum-sealed)

KMPDC0826EB

#### Recommended soldering conditions

KSPDB0419EA

- This product supports lead-free soldering. After unpacking, store it in an environment at a temperature of 30 °C or less and a humidity of 60% or less, and perform soldering within 1 year.

- The effect that the product receives during reflow soldering varies depending on the circuit board and reflow oven that are used. When you set reflow soldering conditions, check that problems do not occur in the product by testing out the conditions in advance.

- · In order to improve reliability, we recommend that you use underfill resin to fill the gap between the element and the board, after reflow soldering.

#### Related information

www.hamamatsu.com/sp/ssd/doc\_en.html

- Precautions

- · Disclaimer

- · Surface mount type products

- Technical note

- · Distance image sensors S15452/S15453/S15454-01WT, S16443/S16444-01WT

#### Evaluation kit for distance linear image sensor C15356

An evaluation kit [70 mm (H) × 55 mm (V)] is available for the S15452-01WT distance linear image sensor (with the S15452-01WT). Contact us for detailed information.

#### ASIC for distance image sensors H15472-01

The ASIC for distance image sensors is built-in circuits (driver circuit, A/D converter), etc. for I/O of distance image sensors.

Information described in this material is current as of May 2023.

Product specifications are subject to change without prior notice due to improvements or other reasons. This document has been carefully prepared and the information contained is believed to be accurate. In rare cases, however, there may be inaccuracies such as text errors. Before using these products, always contact us for the delivery specification sheet to check the latest specifications.

The product warranty is valid for one year after delivery and is limited to product repair or replacement for defects discovered and reported to us within that one year period. However, even if within the warranty period we accept absolutely no liability for any loss caused by natural disasters or improper product use. Copying or reprinting the contents described in this material in whole or in part is prohibited without our prior permission.

## AMAMATSU

www.hamamatsu.com

HAMAMATSU PHOTONICS K.K., Solid State Division

1126-1 Ichino-cho, Higashi-ku, Hamamatsu City, 435-8558 Japan, Telephone: (81)53-434-3311, Fax: (81)53-434-5184

ILIZO-1 ICRIINO-CRO, HIGBSRI-KU, Hamamatsu City, 435-8558 Japan, Telephone: (1)908-231-0960, Fax: (1)908-231-1218

Germany: HAMAMATSU CORPORATION: 360 Foothill Road, Bridgewater, NJ 08807, U.S.A., Telephone: (1)908-231-0960, Fax: (1)908-231-1218

Germany: HAMAMATSU PHOTONICS DEUTSCHLAND GMBH: Arzbergerstr. 10, 82211 Herrsching am Ammersee, Germany, Telephone: (49)8152-375-0, Fax: (49)8152-265-8 E-mail: info@hamamatsu.de

France: HAMAMATSU PHOTONICS FRANCE S.A.R.L.: 19 Rue du Saule Trapu, Parc du Moulin de Massy, 91882 Massy Cedex, France; Telephone: (33)1 69 53 71 00, Fax: (33)1 69 53 71 10 E-mail: info@hamamatsu.df

United Kingdom: HAMAMATSU PHOTONICS UK LIMITED: 2 Howard Court, 10 Tewin Road, Welwyn Garden City, Hertfordshire, AL7 18W, UK, Telephone: (44)1707-2925777 E-mail: info@hamamatsu.co.uk

North Europe: HAMAMATSU PHOTONICS NORDEN AB: Torshamnsgatan 35, 16440 Kista, Sweden, Telephone: (46)8-509-031-00, Fax: (46)8-509-031-01 E-mail: info@hamamatsu.de

Taly: HAMAMATSU PHOTONICS (TAILA S.R.L.: Strada della Moia, 1 int. 6 20044 Arese (Milano), Italy, Telephone: (46)8-509-031-01 E-mail: info@hamamatsu.it

China: HAMAMATSU PHOTONICS (CHINA) CO., LTD.: 1201, Tower B, Jiaming Center, 27 Dongsanhuan Bellu, Chaoyang District, 100020 Beijing, PR. China, Telephone: (86)10-6586-6006, Fax: (86)10-6586-6066, Fax: (86)10-6586-6006, Fax: (86)1